基于FPGA的DDR3控制器设计

摘要 介绍了DDR3 SDRAM的技术特点、工作原理,以及控制器的构成。利用Xilinx公司的MIG软件工具在Virtex-6系列FPGA芯片上,实现了控制器的设计方法,并给出了ISim仿真验证结果,验证了该设计方案的可行性。

本文引用地址:http://www.eepw.com.cn/article/201609/303621.htmDDR3 SDRAM是第三代双倍数据速率动态同步随机存储器的简称。是SDRAM内存产品家族中的一员。DDR3内存模组是采用多颗DDR3 SDRAM,并根据JEDEC的相关内存模组设计标准而制作。DDR3SDRAM有如下技术特点:(1)DDR3新增了重置(RESET)功能,并为此新功能设置了管脚,当RESET命令有效时,DDR3将终止所有操作,此时处于活动量最少的状态,以降低功耗。(2)DDR3新增ZQ校准功能,ZQ也是一个新的管脚,这个引脚通过一个命令集及片上校准引擎(On—Die Calihration Engine,ODCE)自动校验数据输出驱动器导通电阻与ODT的终结电阻值。(3)在DDR3系统中,将参考电压分成两个:一个是为地址和控制总线提供服务的VREFC,另一个是为数据总线提供服务的VREFDQ,两个不同的参考电压为DDR3提供更好的抗噪能力。(4)在DDR3系统中,控制器和存储器是一一对应的,由此便可大幅减轻地址、控制、数据信号的总线负担,提供了信号的完整性。这是DDR3和DDR2的一个关键区别。对单个Rank的模组,控制器和内存是点对点(Point to Point)的连接关系,对双Rank的模组,控制器和内存是点对双点(Point to 2Points)的连接关系。(5)DDR3存储器模块的地址、命令、控制信号和时钟采用了“Fly—by”的拓扑结构,大幅减轻了地址、命令、控制和数据总线的负载,提高了信号的完整性。

1 DDR3 SDRAM工作原理

系统上电后,在DDR3 SDRAM进行正常读写操作前,必须按照规定步骤完成初始化操作,然后才能进入空闲的状态,等待控制器的访问。初始化操作过程中主要完成对模式寄存器的配置工作,DDR3芯片上有4个模式寄存器,通过模式寄存器的配置,可完成比如突发长度、读取突发种类、CAS长度、测试模式、DLL复位、输出驱动能力等的设置。

DDR3 SDRAM的工作状态转换是通过指令来实现的,主要通过CS#(片选信号)、RAS#(行选通信号)、CAS#(列选通信号)、WE#(读写控制信号)之间的组合状态实现,DDR3 SDRAM支持的命令主要有:

(1)预充电命令。作用是关闭特定Bank中打开的行或者所有Bank中打开的行,SDRAM寻址具有较强的独占性。对于第一次的读写,只需用激活命令打开此行即可,而对于当前行仍处于打开状态,要对新一行进行读写,此时就要关闭当前行,此命令就是预充电命令。

(2)刷新命令。SDRAM单元有个缺点就是用电容存储数据。但由于漏电流的存在,数据不能长时间存在存储单元中,需要周期性的刷新来保持数据,所以在SDRAM进行存储工作时,必须进行刷新操作。刷新间隔和存储芯片的温度有关,刷新方式分为自刷新(SREF)和自动刷新(AREF)。自刷新用于正常模式下,而自动刷新用于低功耗情况下。

(3)激活命令。用于激活所要进行读或者写操作的Bank、行和列。在读或者写命令到达DDR3 SDRAM的行之前,要先对要读或写操作的行用激活命令进行激活。与激活命令一起发送的地址位用于寻找进行操作的Bank和行,与读或写命令一起发送的地址位用于寻找进行操作的起始列单元。

(4)读命令。用于对一个已激活的行进行读操作。在读操作完成之后,被访问的行依然处于打开状态,直到被预充电命令关闭。BA0~BA2用来选择Bank的地址,A0~Ai提供的输入地址用于选择开始列地址,读命令操作如图1所示。

(5)写命令。用于启动一个突发的存储器写操作,由FPGA向DDR3 SDRAM中写入数据。BA0~BA2用于选择Bank的地址,A0~Ai提供的输入地址用于选择开始列地址由FPGA将数据写入DDR3 SDRAM中。写命令操作如图2所示。

DDR3芯片内部控制器中有8个Bank处于开放的状态,Bank开放的顺序由控制器发出的命令决定。若8个Bank均处于开放状态,但还有数据要进入Bank,则最后开放的Bank将被关闭,以打开一个新的Bank。在自刷新时,所有Bank都会被关闭,一旦有预充电命令,Bank就会开放。

2 DDR3 SDRAM控制器设计方案

设计采用Xilinx公司提供的DDR3 SDRAM控制器IP核。采用此方案的好处是缩短开发周期、简化系统设计。设计者只需在Xilinx公司提供的MIG3.92软件工具界面上选择FPGA及DDR3 SDRAM芯片型号、总线宽度、速度级别,设置突发长度、CAS延迟、引脚分配等参数,即可生成DDR3 SDRAM控制器。FPGA芯片采用Xilinx公司的Virtex-6系列XC6VLX240T-1FFG1759C型号,DDR3 SDRAM芯片采用镁光公司的MT8JSF25664HZ-1C4D1,该内存芯片行地址宽度为15位。列地址宽度为10位,Bank地址位宽为3位,总容量为2 GB。设置突发长度为8位,数据宽度为64位,速度级别为-2,时钟频率为400 MHz。

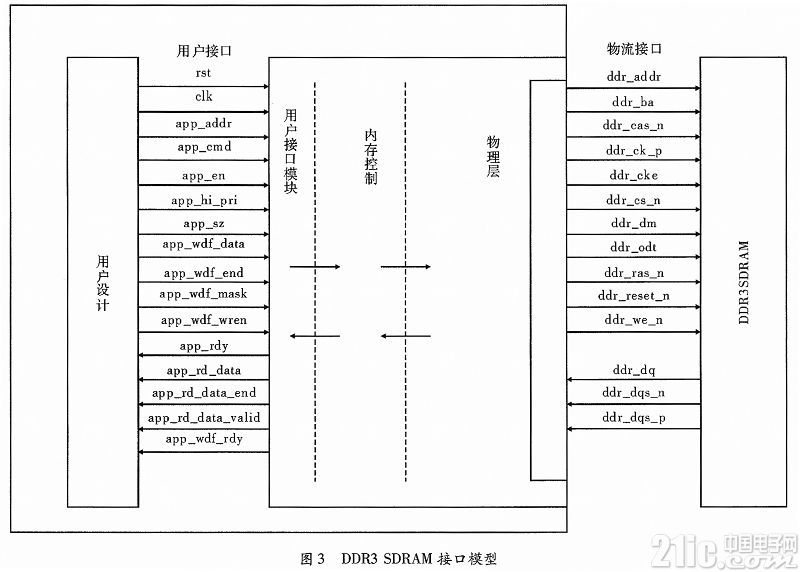

DDR3 SDRAM控制器的主要功能是完成对DDR3SDRAM的初始化,将DDR3 SDRAM复杂的读写时序转化成用户简单的读写时序,将DDR3 SDRAM接口的双时钟数据转化成用户的单时钟数据,并发送周期性的刷新命令来维持DDR3 SDRAM中的数据。控制器主要分为传输层和物理层,传输层负责接收上层用户逻辑的访存请求,并将这些请求转换成DDR3SDRAM所需的时序发送给物理层。物理层负责将控制和地址信号按照DDR3 SDRAM需要的时序发送给存储芯片,同时在传输层和存储芯片之间创建地址通路和数据通路,捕获DDR3 SDRAM发出的数据,通过输入输出缓存发送DDR3 SDRAM所有的控制信号、地址信号以及数据信号,同时保证指令与地址,数据的同步,DDR3 SDRAM接口模型如图3所示。

DDR3 SDRAM内存控制器的设计必须满足两大基本要求:(1)所设计的控制器要实现对内存模组的管理,完成CPU的访存要求。(2)需尽可能提高访问内存的速度和带宽,这是衡量内存控制器性能的重要指标,同时还需考虑内存的兼容性和成本问题。

3 实验结果

为验证DDR3控制器IP核的正确性,对MIG生成的测试模块在ISE14.2环境下进行功能仿真验证,该模块可以对DDR3存储器进行一系列操作,并对写入和读出的数据进行比较,从而验证控制器的正确性。仿真结果如图4所示,phy_init_done的值为1,说明初始化完成。当app_cmd=000时,表示当前进行写操作,只有同时app_en=1和app_rdy=1,app_ addr才能写入成功。当app_cmd=001时,表示当前操作为读操作,可通过rror这一比较信号验证控制器是否正确。从仿真结果可看出,比较信号error始终为低电平,说明写入和读出的数据是一致的。

4 结束语

通过对DDR3的技术特点和工作原理进行分析,将DDR3控制器的从层次上分为传输层和物理层,然后给出了DDR3 SDRAM控制器的设计方法,将控制器在Xilinx公司的Virtex-6系列FPGA芯片上实现,通过ISim软件仿真结果,证明了设计的可行性和正确性,以及IP核设计的DDR3控制器具有较好的适应性和灵活性,缩短了系统开发周期、降低了系统开发成本。

评论