USB2.0接口传输的FPGA控制与实现

2.2.3 应用程序

应用程序是系统与用户的接口,设备驱动程序提供应用程序访问底层硬件的接口。驱动程序采用了CyPress公司的通用驱动程序ezusb.-sys,完全能够满足本系统设计的要求。在驱动程序被系统加载后,它的许多进程处于Idle状态,需要应用程序去调用激活。应用程序利用Win32 API直接调用驱动程序,实现应用程序和驱动程序的信息交互。

应用程序实现了数据下载和数据上传两个功能,在Windows操作系统中,只需要通过调用几条简单的文件操作API函数,就可以实现与驱动程序中USB设备通信。 Win32应用程序调用WDM驱动程序的Win32 API函数有5个:CreateFile(创建设备)函数;CloseFile(关闭设备)函数;ReadFile(从设备读取数据)函数;WriteFile(对设备写入数据)函数;DeviceContronl(设备控制)函数。对于DeviceloControl()函数的调用,驱动程序根据I/O控制命令来决定该如何获取应用程序的缓冲区地址。

本设计就采用DeviceloControl函数来进行应用程序和WDM设备驱动程序间的通信。以下是DevicelIoControl的声明:

DeviceIoControl(

HANDLE hDevice;设备返回的句柄

DWORD dwIoControlCode;驱动程序的控制命令

LPVOID lpInBuffer;应用程序发给驱动程序的缓冲区地址

DWORD nInBufferSize;应用程序发给驱动程序的缓冲区大小

LPVOID lpOutBuffer;驱动发给应用程序的缓冲区地址

DWORD lpOutBuffer;驱动发给应用程序的缓冲区大小

LPDWORD lpBytesReturned;存放驱动程序实际返回字节数

LPOVERLAPPED lpOverlapped;同步时置为NULL)本文引用地址:https://www.eepw.com.cn/article/202550.htm

3 测试结果

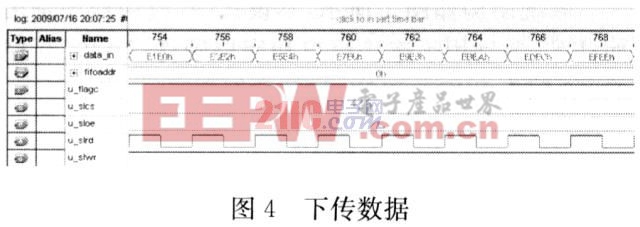

3.1 PC下传数据

FPGA采用系统时钟为50 M,为便于计算传输效率和传输可靠性,在应用程序中加载计时函数,下传数据每次发送100M,发送数据为位宽8 b的循环递增数列,结果显示下传数据最大速率为42.1 MB/s,在FPGA中用嵌入式逻辑分析仪查看接收的数据,如图4所示。每个u_slrd读脉冲,FPGA读取一个16 b数据,由于发送时是按照8 b发送,接收数据是16 b,所以每次接收到的16位数据,是2个8位数的组合。从图4中可以看出FPGA接收数据准确,无丢失数据的情况。

3.2 PC接收数据

在接收数据时,同理,应用程序每次接收100 M,将读取的数据以文件bin的形式存储在应用程序工程目录下,结果显示bin文件中数据准确。测得最大传输结果为 38.4MB/s,利用FPGA嵌入式逻辑分析仪分析结果如图5所示,每个u_slwr读脉冲,FPGA发送一个16 b数据。

4 结束语

本系统通过FPGA控制USB2.O控制器CY7C68013达到高速数据传输的目的,具有硬件结构简单、软件扩展性强、传输数据准确性高等特点,目前下传和上传速度分别为42.1MB/s和38.4 MB/s,完全可以应用于高速数据采集、高速数据通信、数字摄像设备及存储设备等。

评论