USB2.0接口传输的FPGA控制与实现

2 系统的设计实现

系统结构如图l所示,本设计中,应用程序是用户界面;USB驱动用于连接用户和底层硬件;USB2.O控制器68013用于FPGA和PC间的数据交互。

2.1 硬件结构

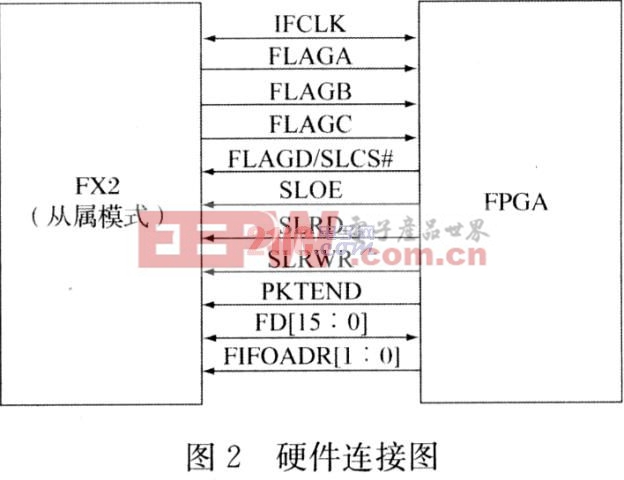

本系统硬件连接主要是由FPGA和USB2.0控制器,如图2所示。同时也可以根据实际系统的需要,用FPGA实现预定功能,硬件接口模式有Slave FIFO和GPIF两种接口模式。本方案采用Slave FIFO模式,当EZ-USB FX2工作于Slave FIFO时,外围电路可像普通FIFO一样对FX2中的端点2、端点4、端点6、端点8的数据缓冲区进行读写。图2展示了这种模式下FX2和外围电路的典型连接,其中,IFCLK为接口时钟,可由芯片CY7C68013产生(30 MHz/40 MHz),也可由外部输入(5MHz/48 MHz);FLAGA-FLAGD为FIFO标志管脚,用于映射FIFO的当前状态;SLCS#为从属FIFO的片选信号,低电平有效;FD[15∶O]为16位双向数据总线;FIFOADDR[1∶O]用于选择和FD连接的端点缓冲区;SLOE用于使能数据总线FD的输出;SLRD和SLRWR可分别作为FIFO的读写选通信号;外围电路可通过使能PKTEND管脚向USB发送一个IN数据包,而不用考虑该包的长度。

2.2 系统软件

系统软件设计主要包括3部分:VHDI代码、USB固件程序(Firmware)以及应用程序。

评论