满足芯片生命周期扩展需求

在当今竞争激烈的商业环境中,驾驭复杂性可能是一个决定性的优势,但同时也带来了重大挑战。推动复杂性增加的三个关键趋势是技术扩展、设计扩展和系统扩展。传统上,可测试性设计 (DFT) 解决方案侧重于晶片级别;然而,这些挑战在封装和系统层面也带来了机遇。为了有效地满足客户需求,Siemens EDA 采取了积极措施来应对他们遇到的挑战。通过利用创新的芯片生命周期管理 (SLM) 解决方案,他们成功地大规模部署了高级系统,使客户能够在竞争激烈的市场中蓬勃发展。

图 1:影响半导体制造商的三大扩展挑战。半导体公司可以利用验证和确认阶段的数据来创建其芯片和系统的真正数字孪生。这种方法为获得有关性能、可靠性、安全性和安全性的数据驱动型见解开辟了新的可能性。

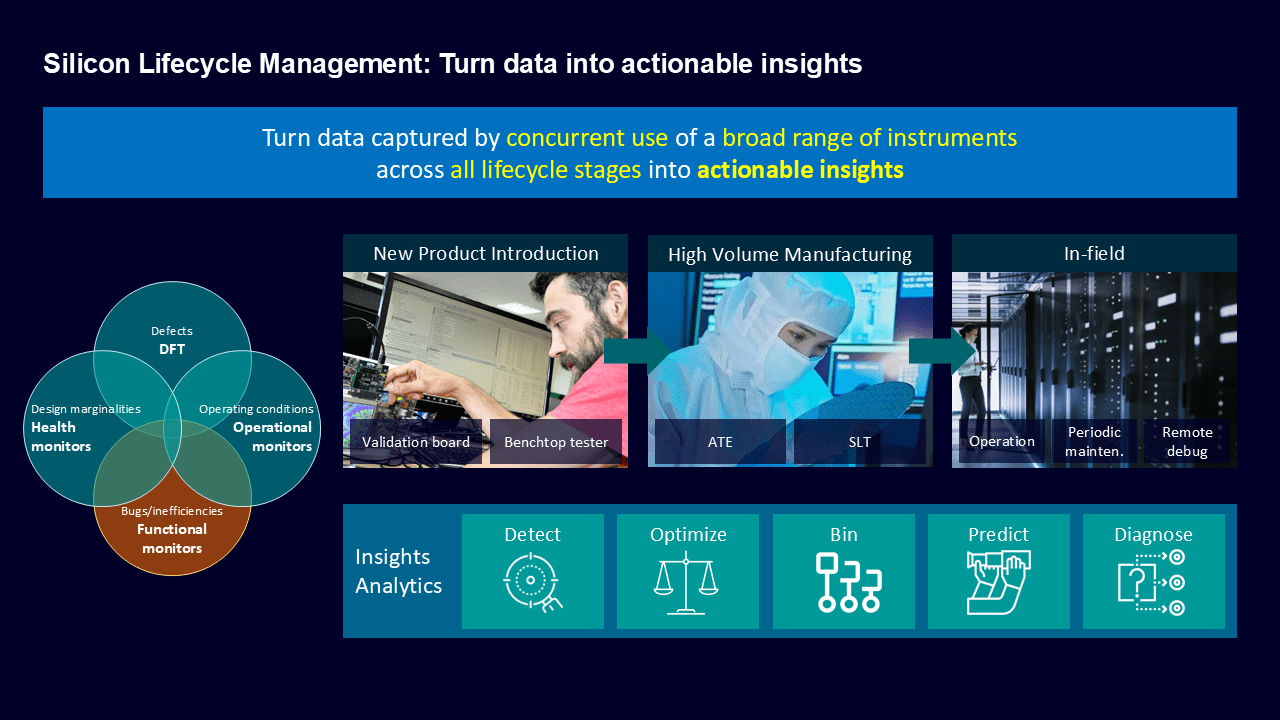

Siemens EDA 在芯片和系统的整个生命周期中采用统一方法,为新的应用程序和可见性提供支持。其 SLM 战略可帮助半导体公司充分利用复杂性的竞争优势,而不会影响性能。SLM 解决方案提供了一个全面的基础设施,可显著提高设计可测试性,提供卓越的测试质量,同时发现缺陷和隐藏的良率限制因素。通过从测试无缝过渡到系统调试和验证,这些解决方案确保了强大的最终产品。此外,它们集成了所有这些功能,以实现持续的实时监控,从而提供无与伦比的可靠性和性能。

这种整体 SLM 方法的底线好处是巨大的。IC 设计和生产过程变得更加灵敏、敏捷和成本效益更高。设备更容易集成到最终产品中,并且在部署后更加可靠和安全。在设备的整个生命周期内监控重要事项的能力,可在现场实现预防性维护和持续性能优化。

图 2:芯片生命周期管理流程。

SLM 是西门子使用数字孪生来应对复杂挑战并有效推动创新的战略的关键要素。产品的数字孪生是实际产品的虚拟表示。它允许在创建物理版本之前在虚拟环境中设计和验证产品。

数字化转型是一个持续的过程,即使对于已经数字化数十年的公司也是如此。Siemens 的软件和全面的数字化双胞胎使公司能够优化其设计、工程和制造流程。

自动化对技术扩展至关重要

SLM 解决方案本质上是多领域的,因此为 DFT、收益分析和功能监控活动采用最佳实践至关重要。SLM 有助于在现场部署芯片后从芯片中无缝收集数据,并搭配一套强大的数据分析和解释工具。这种组合不仅提供了对系统性能的重要见解,还使组织能够提高可靠性并推动创新。

技术和系统复杂性推动了对增强故障建模和检测的需求,特别是对于较新的故障类型,例如系统设计错误 (SDE) 和静态数据损坏 (SDC) [1]。这些故障不仅取决于晶体管级效应,还取决于系统级条件,包括潜在缺陷、老化和软件工作负载对电力传输的影响。因此,检测制造过程中和最终产品内部的故障变得至关重要。如果公司不升级到先进的 DFT 工具和方法,那么在先进技术节点上设计的片上系统 (SoC) 可能难以满足当今市场要求的高质量标准。

自动化,尤其是当它可以实时适应和优化时,是设计过程的一个关键方面。技术扩展的主要目标是实现自动化的精度和保真度,从而推动创新并提高效率。通过采用 Tessent Diagnosis 中提供的面向缺陷的检测和细胞感知诊断功能,我们可以实现有效建模、检测和诊断物理缺陷所需的准确性。然而,这种增强的缺陷识别能力也使模式生成过程复杂化,需要创建额外的测试模式。

用于设计扩展的数据包化扫描交付

设计中晶体管的困难源于设计复杂性的增加,特别是在尺寸和与 DFT 实现相关的成本方面。这种复杂性导致 Core 和 Block 上的并行工作增加,以及重复 Core 使用量的增加。一种常见的方法是在 block 级别完成物理设计,然后将这些 blocks 相邻在一起,这被称为基于 tile 的设计流程。但是,这种趋势使传统的 DFT 实施过程复杂化。

分层 DFT 流多年来一直有效,使 DFT 能够集成并在块或核心级别生成模式。然后,这些可以映射到顶层。遗憾的是,相同内核数量的增加以及基于磁贴的流的使用(缺乏顶级逻辑)使得分层流更具挑战性。这些挑战包括规划工作、带基台的平铺设计、测试成本、布线和时序收敛。

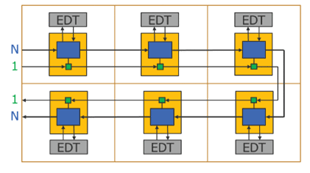

分组扫描交付解决了与复杂 SoC 中的扫描分发相关的许多挑战。这种方法允许同时测试多个内核,同时仅使用几个芯片级引脚。它可以在几乎恒定的时间内有效地测试任意数量的相同核心实例,从而减少对填充的需求,即使核心具有不同的码型计数或扫描链长度。

Siemens EDA 的 Tessent TestKompress 和流式扫描网络 (SSN) 解决方案提供分组扫描交付。这些系统旨在解决测试 SoC 设计中的常见 DFT 挑战,将核心 DFT 优化与集成到设计中分离,提供可用的输入/输出接口。这种方法有效地将测试交付与核心级 DFT 要求分离。例如,在内核级压缩中,可以完全根据芯片 I/O 限制来定义配置。关于将同时测试哪些内核的决定是通过编程方式做出的,而不是像传统的引脚多路复用方法那样硬连接。

图 3:分组扫描交付架构。

数据包扫描交付的另一个优势是其自适应智能。在 DFT 设计最终确定并生成测试模式后,可以选择要测试的特定内核。一旦用户确定了要测试的内核,数据包交付过程就会得到优化,以确保尽可能高效地交付。

系统扩展

导致复杂性的第三个趋势是系统扩展。随着技术和设计的扩展,越来越多的功能可以在单个集成电路 (IC) 中实现,并且更多的 IC 可以集成到单个封装中。

系统扩展会带来多种挑战,例如:

在流片前优化系统架构

确保功能子系统在芯片中正确协同工作

满足功能规范

管理共享资源的利用率

针对特定硬件实施优化软件

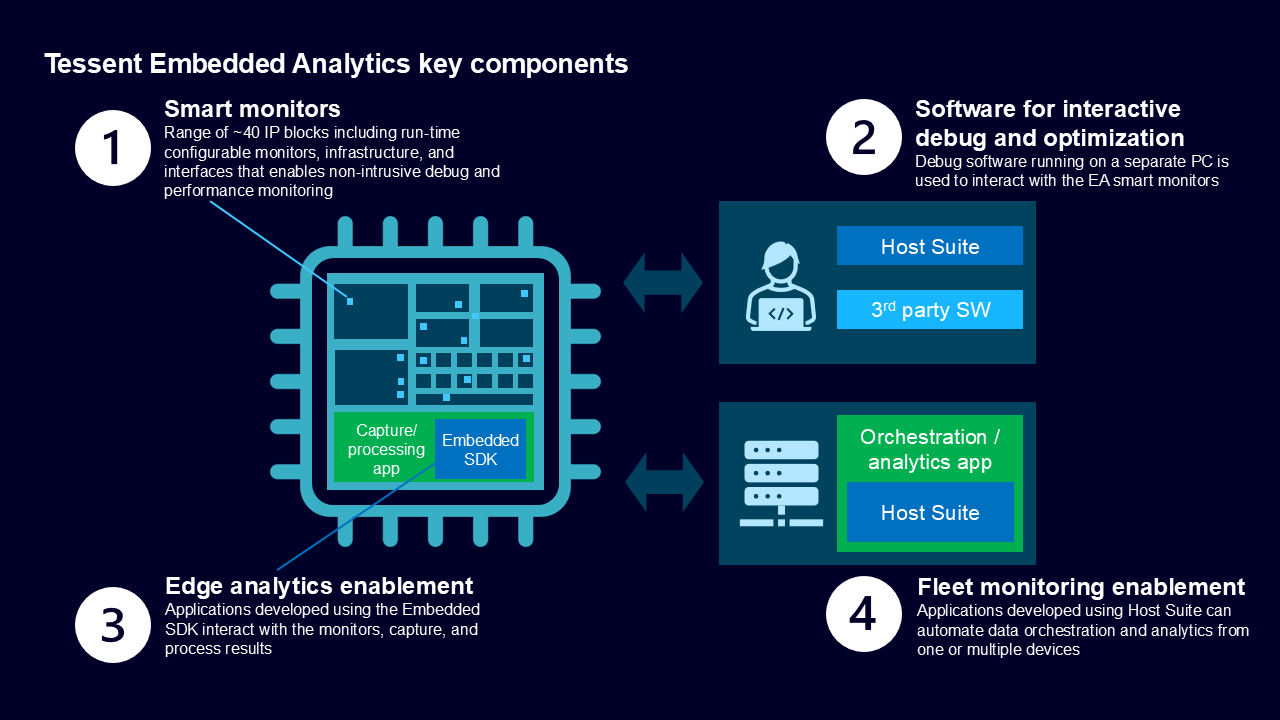

将多个芯片集成到单个产品中变得更加复杂,尤其是在使用将多个小芯片组合到系统级封装中的 3D 集成技术时。一套全面的基于硬件的功能监控工具(以硅 IP 形式提供)可以帮助管理这种复杂性。功能监控应提供芯片的完整概述,以及对每个 IC 子系统的详细见解。它还必须实现硬件和软件的系统级可见性,从而增强 DFT 结构提供的信息。此外,它应该从系统启动的那一刻起就提供准确而有凝聚力的图片。

功能监控还需要根据以下方面提供数据过滤和采集:

可配置的标准

灵活选择感兴趣的子系统

IC 内部的数据预过滤

时间 戳

可编程交叉触发,用于跨不同子系统进行数据关联收集

与系统功能接口兼容的片外数据传输机制

用于构建和集成使用所收集数据的 Analytics 应用程序的工具

为了最大限度地提高功能监控的有效性,必须能够灵活地分析和响应来自分布式系统(片上)和集中式资源(片外)的见解,无论是实时分析还是在额外处理后。最大限度地减少集成到芯片设计中所需的资源和开销非常重要。这些功能有助于数据收集和见解生成,从而提高投资回报率。

图 4:Tessent Embedded Analytics 功能监控解决方案。

Tessent Embedded Analytics 提供的功能监控以及数据收集生成的见解提供了一种独特的自适应智能形式。在这种情况下,它为优化功能作和改进最终产品应用提供了机会。

大规模部署

在开发阶段遇到的许多问题也会在部署 IC 或嵌入式系统后出现。例如,结构测试对于检测与老化相关的可靠性问题或静默数据错误 (SDE) 是必要的。有些问题只有在部署后才会显现出来;在实际软件负载下,可能会出现低概率、高影响的性能问题。必须像任何其他错误一样检测、确定优先级、调查和解决这些问题。

扩展系统的最大挑战之一是硅的老化以及由此产生的固有可靠性问题。通过分析产品整个生命周期中来自 DFT 结构的数据,并将其与部署前阶段收集的类似数据相结合,我们可以识别现场故障并开发老化和可靠性模型。这种方法使我们能够提前预测潜在的故障。此方法的一个关键应用是检测由数据损坏引起的 SDE。

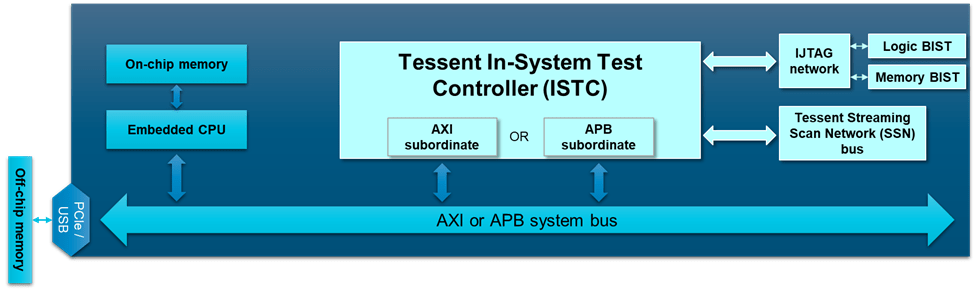

确定性系统内测试已经投入使用,预计采用率会越来越高。它们有助于处理测试数据量的急剧增长。Tessent In-System Test 支持创建高质量、确定性的测试模式。Tessent In-System Test (IST) 是对 Tessent SSN 的补充,增强了其在系统内、现场环境中使用的能力。设计人员可以使用在系统测试控制器,直接通过 SSN 总线应用使用 Tessent SSN 软件生成的嵌入式确定性测试 (EDT) 模式。

图 5: 在系统确定性测试逻辑。

在任何 SLM 解决方案中,都需要对设备进行持续测试和监控,以确保其在整个运行过程中的最佳性能、可靠性和安全性。Tessent In-System Test 支持在芯片的整个生命周期内应用高质量、确定性的测试模式进行系统内和现场测试。

总结

每一次挑战都蕴含着机遇。芯片生命周期解决方案为利用技术、设计和系统扩展趋势的公司提供了显著的优势,尤其是那些大规模部署的公司。芯片生命周期管理涉及在现场部署芯片后从芯片中无缝收集数据。此过程包括一套工具,这些工具可以有效地使用和分析数据,从而提供对系统性能的关键见解。

除了硅级基础设施之外,端到端 SLM 还需要从传统的芯片设计工具工作流程中转变。它需要实施全面的闭环数字孪生概念,这有助于将数据从实时的现场产品传回以进行分析和评估。这些数据可以与设计、开发、仿真、制造和测试的早期阶段相关联。

随着创新步伐继续每年产生更多的数字系统,我们生成的数据呈指数级增长,这些数据可用于分析并可能货币化。这使得数字化转型成为一段持续的旅程,即使对于已经数字化数十年的公司也是如此。

现代系统的复杂性可以通过将应对各种结垢挑战的基础元素与尖端技术集成来解决。最重要的是,当这些基本元素无缝协作时,采用 SLM 解决方案的巨大好处最容易实现。

Siemens EDA 的 Tessent Silicon Lifecycle Solutions 通过使用高质量的 DFT 简化设计复杂性,从而加快上市时间。这些解决方案包括高级调试、安全和信息安全功能,以及实时数据分析,以应对当今芯片生命周期中不断变化的挑战。

评论