西门子EDA用AI工具解决首次流片成功率下降问题

Siemens EDA 强调,整个半导体行业第一枚硅晶圆流片的成功率下降令人震惊。

本文引用地址:https://www.eepw.com.cn/article/202505/470412.htmSiemens EDA(Siemens Digital Industries Software 旗下公司)设计验证技术副总裁兼总经理 Abhi Kolpekwar 表示,首次流片成功率正在下降,从 2022 年的 24% 和 2020 年的 32% 下降到 2024 年的 14%。

“这在 ASIC 和 FPGA 中都是一个令人惊讶和令人震惊的下降,”他说。这是一个非常大的问题,可以追溯到今天人们流片的设计复杂性。

该公司开发了一套互锁的工具,用于使用 AI 代理验证设计,以尝试解决这个问题。

“第二个问题是时序约束。75% 的项目落后于计划。然后,熟练的劳动力只能满足 20% 的需求,因此目前 80% 的需求没有得到满足。

“我的业务就是帮助人们在流片之前对他们的设计进行功能验证,尽快、尽早地发现设计中的任何错误。错误在系统中停留的次数越多,它们的成本就越高,因此游戏计划是在它们便宜的时候尽可能多地捕捉它们,这样人们就不需要重新设计了。

“仅仅生产更快的模拟器是不够的。我们需要更快的引擎、更快的工程师(通过自动化任务和分析)以及更少的工作负载。所有这些都使最终用户的总生产力提高了 5 倍,“Kolpekwar 说。

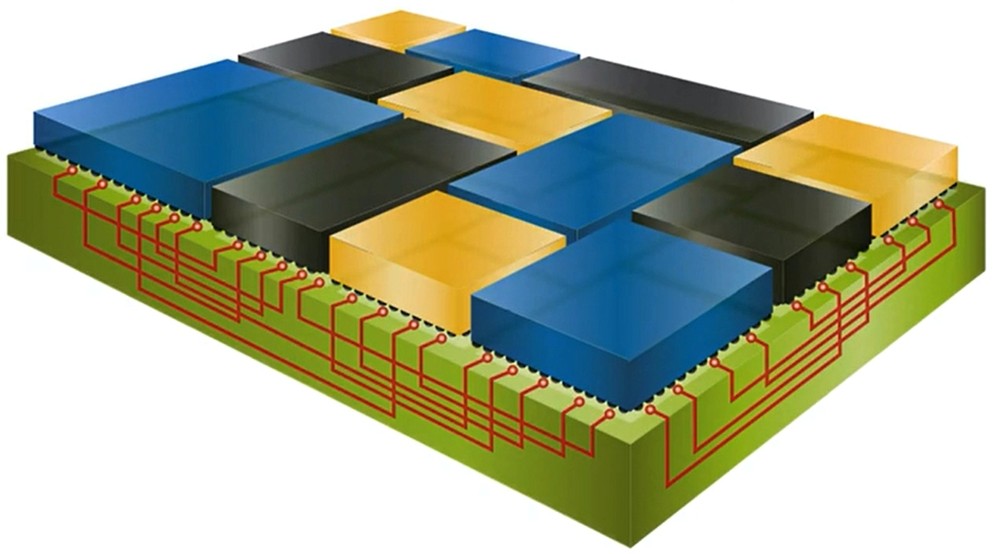

Questa One 具有三个要素,具有新的模拟引擎、验证工具和验证 IP,所有这些都使用生成式 AI 和 AI 代理。这些工具正在被 ARM、Mediatek、Rambus 和 Microsoft 使用。

例如,智能创建工具采用设计要求,并将其转化为设计要求,以便使用 Generative AI 进行形式化验证。智能回归工具可识别故障模式,并使用预测性 AI 快速调试问题。

“您无需运行数千次回归测试,只需针对任何设计更改运行几百次优化测试。此外,还可以预测可能失败的测试用例,并且这些测试用例首先排序,这样如果回归失败,您就不必运行其余的测试,“Kolpekwar 说。“这就是我们使用 AI 来减少工作量的方式。”

智能引擎可以访问所有设计数据库和测试平台,以加速数据计算,加速仿真,而智能调试工具使用 AI 来识别故障并为特定代码提供根本原因分析。

开发了一种新的仿真引擎,支持具有自动分区的并行仿真、功能安全仿真以及静态和动态功耗分析。

AI 在运送给客户之前,会根据 Siemens EDA 中的标准文档进行训练,并且模型将使用带有检索增强生成 (RAG) 的本地训练模型进行训练。

这简化了验证工具链。

“您可以将生成式 AI 代码生成用于测试台,也可以用于运行形式检查器,但这还不够,”Kolpekwar 说。“您可以从设计需求文档中选取部分,并直接从文档中生成断言。”

QuestaOne 验证工具链的另一部分是无激励验证 (SFV),用于静态和形式验证,无需仿真平台即可发现错误。

“SFV 的想法使用 GenAI、LLM、预测和分析 AI 将静态和形式分析相结合,”他说,“而不是在用户提出问题的地方启动 linter,我们应用 linter,找到违规并自动修复,然后运行 RTL 到 TRL 等效性检查。

Verification IQ 工具使用分析 AI 和生成式 AI 来自动执行任务和工作负载。这来自 2023 年对 Avery Design Systems 的收购。

“我们正在构建该基准协议技术,通过验证 IP 生态系统引入测试用例和 AI 应用程序的基础设施。自从我们收购了它们以来,我们已经创建了一个验证 IP 生态系统,在 QEMU 软件仿真和 Veloce 硬件仿真上具有可仿真和可仿真的 IP。

评论