SRAM在新一代IoT和可穿戴嵌入式设计中的作用

面积的缩小可通过取消第一级封装来实现,其中包括引脚框架、管芯连接、焊线以及铸模化合物。CSP芯片大多采用晶圆级封装,将封装材料直接堆放在晶圆片上。引脚分布类似于球栅阵列封装(BGA),封装上的焊接凸点起引脚作用。通过缩小工艺节点可获得类似的尺寸缩小效果。

对于可穿戴应用中空间有限的电路板来说,CSP SRAM明显将是最佳选择。与仅次于它的备选方案(购买一块SRAM管芯,然后使用高级多芯片封装(MCP)技术将它与MCU管芯封装在一起)相比,将 CSP SRAM纳入设计要便捷得多。目前,CSP SRAM还没有投入量产,有些供应商将其作为定制选项提供,可能是因为目标市场(可穿戴)还没有超越嵌入式领域。不过在 SRAM 市场中,大多数主要厂商都可为他们的很多其它产品提供CSP选项。例如,赛普拉斯半导体已针对其PSoC等产品系列提供了CSP版本。因此,对于制造商来说,将这种功能延伸至SRAM应该不难。

引脚数更少

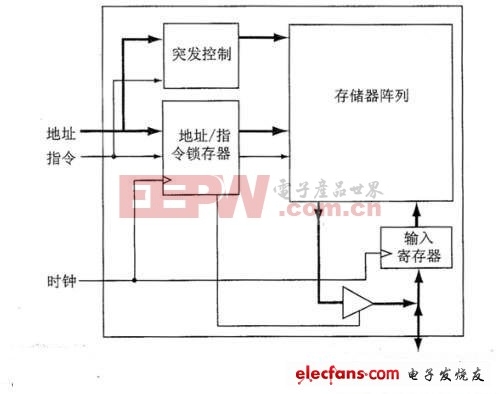

在SRAM的功耗低于闪存和DRAM时,使用SRAM进行存储器扩展的主要问题是其并行接口。尽管并行接口能实现更快的读写速度,但有太多的IO需要连接。例如,如果将一个1Mb SRAM (64Kb x16) 与一个MCU连接,所需的IO数量将会是32个(16个地址,16个数据)。进行多路复用可将该数字减少至24。但容量每增加一级(2M、4M、8M 等),引脚数就会增加1个。

极小可穿戴电路板上用来连接SRAM的IO数量有限,因为小型MCU的封装引脚数量少。要与这些MCU连接,SRAM必须突破传统的并行接口。串行闪存和EEPROM等的成功增强了串行存储器选项的市场需求。MCU使用嵌入式高速缓存已有很多年了,因此对于串行SRAM的需求直到最近几年才被发觉。串行SRAM可实现更便捷的接口连接,更少的引脚使用(单路SPI用两个,双路SPI用两个,四路SPI用四个)。此外,所需的IO数量不会随容量增加而增多。

目前,我们的串行SRAM容量低,存取速度相对较慢(存取时间达25ns,容量为1M)。在不久的将来,我们将有望刷新这两个参数。随着可穿戴产品进入全新时代,我们可能会希望MCU完成更为复杂的工作。在这种情况下,具有更高吞吐量的更高容量高速缓存/高速暂存存储器会十分有用。因此,串行SRAM 向更高速和更高容量的方向发展将对该市场十分有利。使用CSP封装缩小尺寸再加上串行接口,SRAM将会成为可穿戴产品中高速缓存及高速暂存存储器的强大选项。

高性能,低功耗

当前有两个不同系列的异步SRAM:快速SRAM(支持高速存取)和低功耗SRAM(低功耗)。从技术角度看,这种权衡是合理的。在低功耗SRAM 中,通过采用特殊栅诱导漏极泄漏(GIDL)控制技术控制待机电流来控制待机功耗。这些技术需要在上拉或下拉路径中添加额外的晶体管,因此会加剧存取延迟,而且在此过程中会延长存取时间。在快速SRAM中,存取时间占首要地位,因此不能使用这些技术。此外,要减少传播延迟,需要增大芯片尺寸。芯片尺寸增大会增大漏电流,从而增加整体待机功耗。

到目前位置,典型SRAM应用接受这种权衡:电池供电应用使用低功耗SRAM(降低性能),有线工业高性能应用则使用快速SRAM。不过,对于物联网及其它众多高级应用来说,这种权衡不再适用。主要原因是对于大部分这些应用而言,不仅高性能很重要,同时还必须限制待机功耗,因为这些应用大多采用电池供电工作。非常幸运的是,SRAM正在缩小这两个系列之间的性能差距,正逐渐发展成具有这两种优势的单芯片产品。

微控制器很久以前就有了深度睡眠工作模式。这种工作模式有助于为大部分时间都处于待机状态下的应用省电。该控制器可在正常工作中全速运行,但事后则进入低功耗模式,以便节省电源。使所连接的SRAM也具有类似的工作模式很重要。具有深度睡眠工作模式[5]的异步快速SRAM是这类应用的理想选择。这种 SRAM芯片有一个附加输入引脚,有助于用户在不同的工作模式(正常、待机和深度睡眠)间切换。因此可在不影响性能的情况下管理低功耗。 http://www.cypress.com/?docID=48906。

片上纠错功能

存储器工艺技术的提高可改进性能与功耗,因此更低的电压和更小的节点电容会让这些器件更容易出现软错误。如今,CMOS 工艺已经缩小了尺寸,地外辐射和芯片封装都会导致越来越多的故障。一般使用纠错码(ECC)软件或冗余(即多个SRAM存储相同的数据)方式应对软错误,特别是在可靠性一直都极为重要的系统中,例如医疗、汽车和军事系统。然而,这种方式非常昂贵,需要额外的电路板空间。

主要SRAM制造商现已开始直接在芯片上实施纠错特性[6]。要在现代芯片级半导体存储器上限制软错误影响,可使用两种架构增强方法:片上ECC和位交错。通过片上ECC,便可将用于实施错误检测和单个位错误校正的软件硬编码在SRAM中。有些制造商甚至还提供一个额外的错误引脚选项,用以指出单个位错误的检测与校正情况。

另一方便,位交错可用来限制多位错误的影响(即单个能量粒子翻转多个位)。位交错的工作方式是将相邻的位线安排至不同的字寄存器。这样可将多位错误转换为多个单个位错误,随后可通过片上ECC进行校正(进一步了解如何减少和校正软错误)。

SRAM与未来

SRAM技术将迎来激动人心的全新时代。技术趋势与发展都有利于该技术回暖,扭转多年来使用量下降的颓势。支持ECC功能的芯片现已投入量产。支持片上电源管理的快速SRAM也已上市。此外,串行SRAM也已投入量产,但大多数都支持低容量应用,因此目前在速度上还无法与并行方案相匹敌。不过,串行市场的现有厂商(Microchip和On-semi)恰好主要都是MCU制造商。传统SRAM公司尚未推出串行SRAM。随着更多公司进入该市场,我们将有望看到创新技术的快速出现。

关于产品生命周期的传统市场观点是:产品成熟期过后就是衰退,然后是消亡。从SRAM每年的负复合增长率以及大多数供应商退出该市场的事实来看,该产品应划为“衰退”期。然而不管是今天我们目睹的SRAM复兴,还是针对未来预测的,都需要我们重新审视普通产品生命周期的传统理念。

参考资料

1. 维基百科:半导体器件制造

2.《22nm工艺对SRAM内中子引起的软错误的影响》作者:EishiIbe、Hitoshi Taniguchi、Yasuo Yahagi、Ken-ichi、Shimbo和Tadanobu Toba

评论