基于FPGA设计EnDat编码器数据采集后续电路

1.3 时序和OEM数据存储

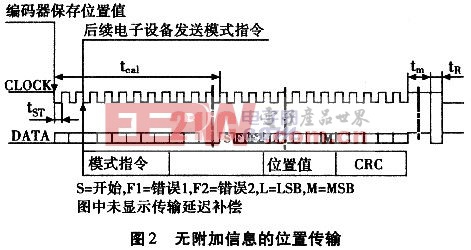

在每一帧同步数据传输时一个数据包被发送,传输循环从时钟的第一个下降沿开始测量值被保存,计算位置值。在两个时钟脉冲(2T)后,后续电子设备发送模式指令“编码器传输位置值”(带或不带附加信息)。在计算出了绝对位置值后(见图2),从起始位开始编码器向后续电子设备传输数据,后续的错误位F1和F2(只存在于EnDa2.2指令中)是为所有的监控功能和故障监控服务的群组信号,他们的生成相互独立,用来表示可能导致不正确位置信息的编码器故障。导致故障的确切原因保存在“运行状态”存储区,可以被后续电子设备查询。

从最低位开始,绝对位置值被传输,数据的长度由使用的编码器类型决定。传输位置值所需的时钟脉冲数保存在编码器制造商的参数中。位置值数据的传输以循环冗余检测码结束。

位置值如果带附加信息,紧接在位置值后的是附加信息1和2,他们也各以一个CRC结束(见图3)。附加信息的内容由存储区的选择地址决定,然后在后面的采样周期里被传输。在后续的传输中一直传输该信息,直到新的存储区被选择。在数据字的结尾,时钟信号必须置高电平。10~30μs或1.25~3.75μs(EnDat可编程的恢复时间tm)后,数据线回到低电平,然后,新的数据传输可在新的时钟信号下开始。

同时,编码器为参数提供了不同的存储区,它们可以被后续电子设备读取,这些区域可以被编码器制造商、OEM厂商甚至最终用户写入。一些特定的区域是可以被写保护的。不同系列的编码器支持不同的OEM存储区和不同的地址范围。因此,每一个编码器必须读取OEM存储区的分配信息。基于此原因,后续电子电路应基于相对地址编程,而不能使用绝对地址。

2 EnDat接口后续电子设备的电路设计方案

全数字化交流伺服系统中采用TMS320F2812作为控制器,用以实现位置环、速度环和电流环以及SVPWM、电压和电流采样等功能。此外,采用Altera公司的型号为EPlC6Q240C8的Cyclone系列FPGA实现与编码器接口、译码逻辑等功能。同时,在FPGA内部实现了128B的双口RAM,通过总线实现与DSP之间的数据传输,功能框图如图4所示。

评论