基于FPGA的数据采集系统的设计与实现

2 数据采集系统软件设计方案

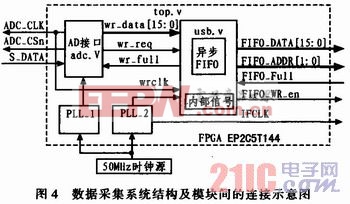

FPGA软件设计方案中采用了自顶向下的设计方法,运用Verilog HDL语言来设计数字系统,分别完成数字系统内部各个子模块的设计。数据采集系统结构及模块间的连接示意图如图4所示。

由图4可见,系统主要由3个模块组成。它们分别是A/D接口adc.v模块、USB接口usb.v模块以及顶层top.v模块,其中在顶层top.v模块中,完成了对其他两个模块的调用,使它们拼接成为一个完整的系统。其中锁相环PLL_1和PLL_2分别给ade.v模块和usb.v模块提供时钟源。

2.1 FPGA控制A/D芯片接口的软件设计

在adc.v模块中,需要完成FPGA对TLV1572的接口逻辑代码的设计,其实质就是在TLV1572的时序分析的基础上来设计逻辑代码,使得FPGA能够按照其时序要求完成对A/D芯片的各种控制,包括提供给TLV1572的串行时钟信号信号ADC_CLK、CS片选信号ADC_CSn以及从TLV1572中读取出转换完成的串行数据S_DATA。

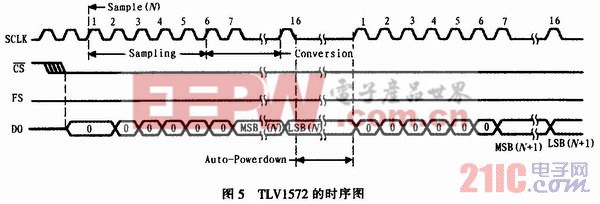

TLV1572的时序图如图5所示。

从时序图可见,A/D芯片的转化过程是在当CS为低电平后,由SCLK的上升沿发起的,输出的头六位二进制数字均为“0”,此时A/D芯片正处于采样阶段,数字无效,这六位无效的二进制数之后,A/D转换完成后的二进制数据在SCLK的上升沿被送到总线上,这时,作为系统主控制芯片的FPGA应当去采样总线上的数据,得到转换后的结果。

2.2 FPGA控制USB2.0芯片的软件设计

在usb.v模块中,需要完成FPGA对CY7C68013A的接口逻辑代码的设计和异步FIFO模块的设计。其中,对CY7C68013A的接口逻辑代码主要是完成对CY7C68013A芯片的端点FIFO的各种控制,包括16位的数据信号FIFO_DATA[15:0]、2位端点FIFO选择信号FIFO_ADDR[1:0]、端点FI-FO满标志位信号FIFO_Full、端点FIFO写使能信号FIFO_WR_en。因为adc.v模块和芯片外部的CY7C68013A工作在不同的时钟域内,故异步FIFO模块设计部分设计的目的除了是要完成从ade.v模块读取过来数据的缓冲,另外就是需要解决异步时钟域数据传输可能出现的亚稳态问题。

具体来说,FPGA在工作时需要不断向CY7C68013A的端点FIFO写入数据,而FPGA与CY7C68013A之间的工作模式属于同步方式,两者都由PLL _2模块提供40 MHz的时钟信号进行工作,那么它们之间的关系就是同步Slave FIFO的写操作,由FPGA向CYTC68013A中写入数据。

在Verilog HDL程序设计中,需要设计一个状态机来完成同步Slave FIFO写的时序,写时序如下;1)IDLE:当写事件发生时,进状态1;2)状态1:使FIFOADR[1:0]指向IN FIFO,进状态2;3)状态2:如果端点FIFO满,在当前状态等待,否则进状态3;4)状态3:驱动数据到数据线上,使SLWR有效,持续一个IFCLK周期,进状态4;5)状态4:如需传输更多的数,进状态2,否则进入IDLE状态。

该状态转换的状态图如图6所示。

评论