基于FPGA的线阵CCD驱动时序及 模拟信号处理的设计

4.2 AD9826时序设计及仿真

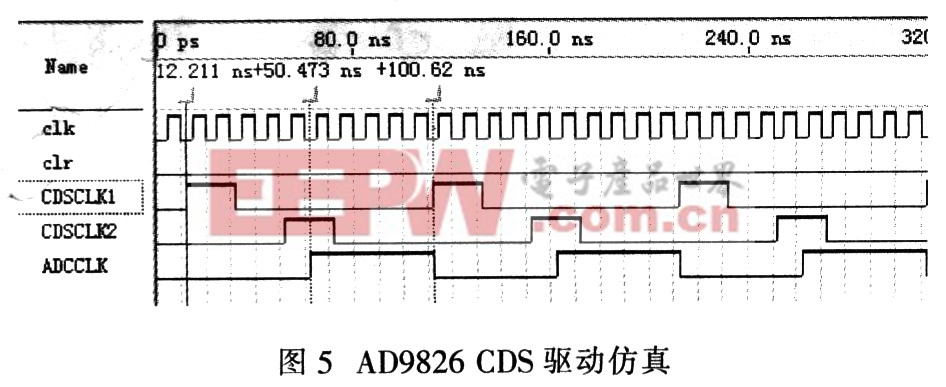

通过对AD9826单通道CDS采样时序分析,结合TCDl501D输出信号的特点,设计出正确合理的CDS驱动时序是保证该器件正常工作的基础。充分利用硬件编程语言(VHDL)的优点,产生各项时序。依据TCDl501D输出信号OS的时序要求及AD9826对CDS的要求,可设定各脉冲的参数为:主时钟为100 MHz,CDSCLK1=CDSCLK2=10 MHz,占空比为l:4,两次采样间隔为40 ns,均为下降沿采样;AD―CCLK=10MHz,占空比为1:l,低电平有效。编译后通过波形仿真的结果如图5所示,其中12.211 ns线为基准,+100.62ns线为相对基准线的偏移量,可知CDSCLKl周期为100 ns,满足器件手册中所规定的要求。

5 结语

通过对TCDl50lD输出图像信号特征的简要分析,分别阐述了内、外2种除噪方法,并给出了相应的时序,再利用Quartus II 7.2软件平台对TCDl501D CCD驱动时序及AD9826的采样时序进行了设计及结果仿真,使CCD的驱动变得简单且易于处理,这是传统逻辑电路无法比拟的,对其他CCD时序驱动及后续处理提供了一定的参考价值。

评论