FPGA异步FIFO设计中的问题与解决办法

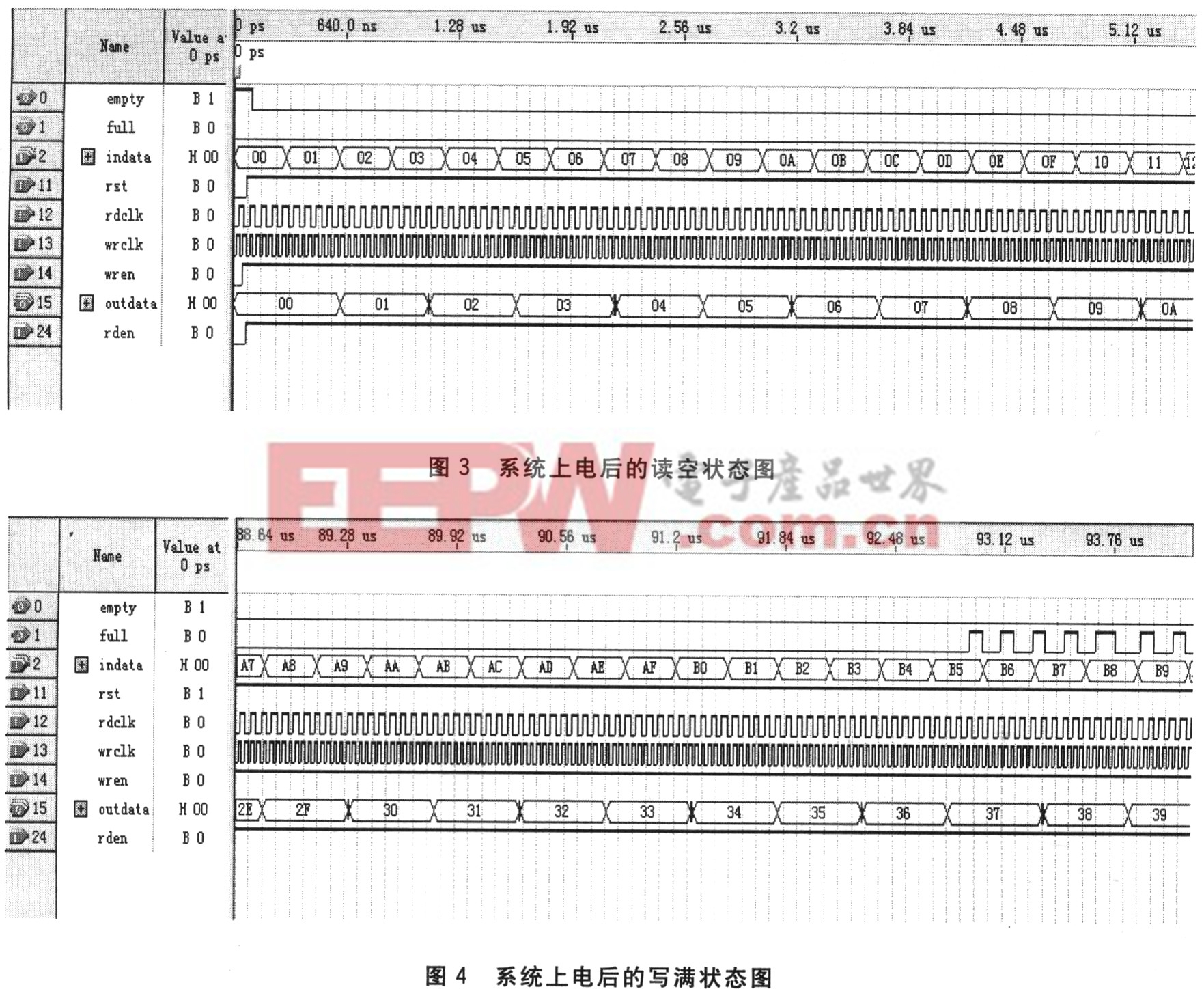

本系统采用QuartusIl8.1对系统进行仿真,由于系统深度较大,所以设定仿真时间为100 μs。系统刚上电时,双端口RAM中暂时没有数据,此时系统处于读空状态,empty变为高电平,full保持低电平,如图3所示。随着RAM中数据的不断写入,系统进入写满状态,此时full变为高电平,而empty变为低电平,如图4所示。本文引用地址:https://www.eepw.com.cn/article/191924.htm

结 语

本文根据异步FIFO设计的难点和要点,提出了具体的解决方案。在空/满标志位产生条件的判断上提出了“检测+计数器”的新思路,使系统设计方便实用,并采用格雷码方式降低了亚稳态出现的概率。通过验证,这种方法在有效判断空/满标志位方面有很大的优势。

评论