出租车计价器的FPGA设计

用Verilog HDL编写程序来实现模块功能的优点在于,当出租车的计费标准发生变化时,可以很容易地通过改写程序来完成新的设计,比起硬件电路的修改要方便得多,这也是用Verilog HDL来实现模块功能的重要优势。

2.2 三位BCD码加法器

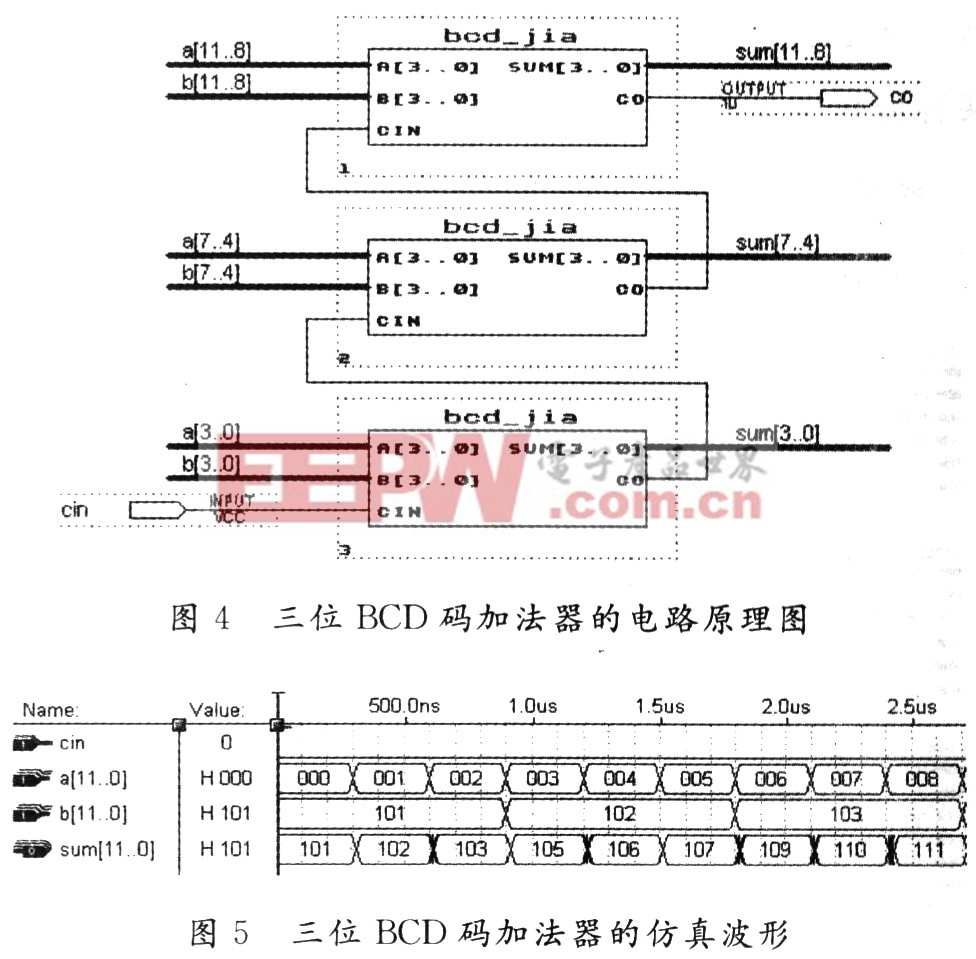

系统中用到了三位BCD码加法器,可以实现三位十进制数的加法运算。加法器输出的结果就是乘客应付的费用,这里同样以前两位为整数,第三位为小数,也就是最大能显示99.9元。三位BCD码加法器由三个一位BCD码加法器级联而成。

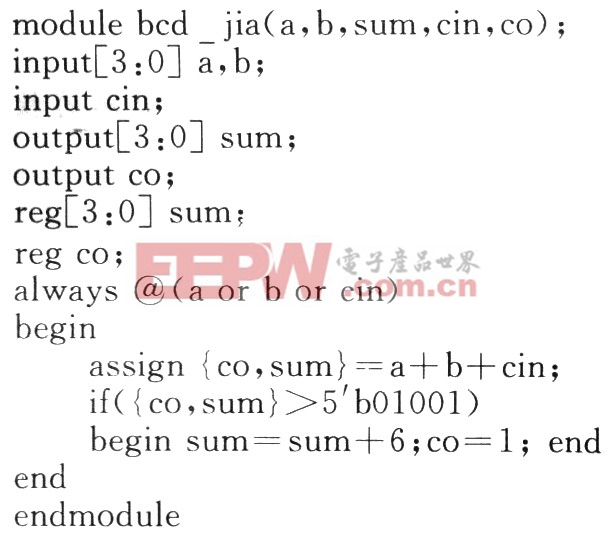

一位BCD码由四位二进制数组成,四位二进制数的加法运算会产生大于9的数字,必须进行适当的调整才会产生正确的结果。一位BCD码加法器的Verilog HDL源程序如下:本文引用地址:https://www.eepw.com.cn/article/191828.htm

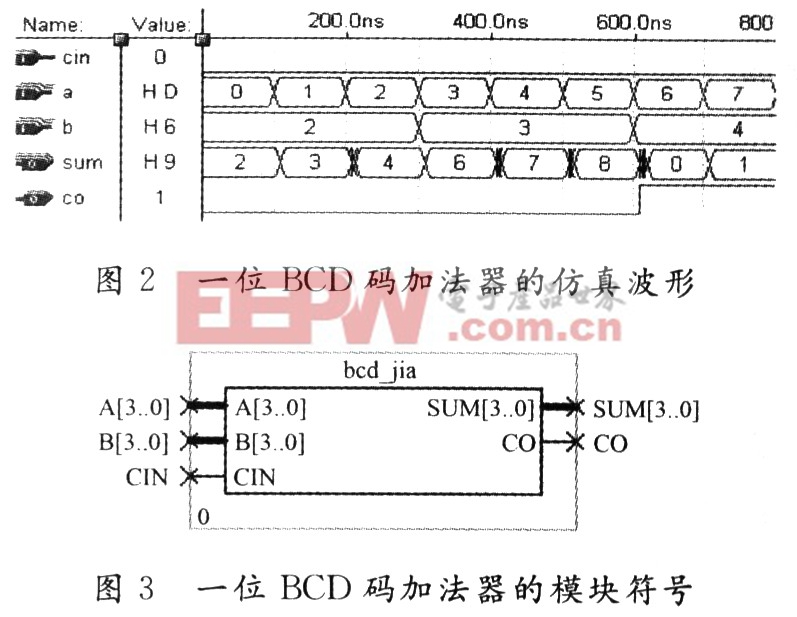

一位BCD码加法器模块的仿真波形和生成的模块符号如图2和图3所示。

本模块中A和B为输入的一位BCD码,CIN为低位来的进位信号,CO是本片向高位产生的进位输出信号,SUM是两个数相加的和。三位BCD码加法器由三个本模块级联而成,其电路原理图和仿真波形如图4和图5所示。

评论