基于FPGA设计DSP的实践与改进

当 DSP Builder模型与仿真都正确后就可以进入模型向硬件描述语言的过程了。加入Signal Compiler模块,点击执行将模型文件转化为硬件描述语言。转换后 DSP Builder的Signal Compiler模块会自动生成 Quartus II的工程,其中的代码已经依据模型自动生成并建立了顶层模块[6]。如图 5。增加相应的输入与输出,锁定引脚后就可以下载了。

本文引用地址:https://www.eepw.com.cn/article/191788.htm

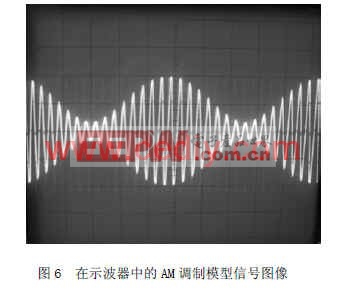

本文引用地址:https://www.eepw.com.cn/article/191788.htm下载到 FPGA中,连接示波器,观察到如图 6所示图像。

4 结语

从实践结果和系统的总体设计方案可以看出,改进的设计流程使得设计人员可以借助Simulink进行灵活的系统模型设计并且可以通过 MATLAB强大的计算能力进行系统级的仿真。由DSP Builder进行硬件描述语言的自动生成让设计者可以更加专注于系统的整体设计,提高了开发效率和系统建立质量。

评论