基于FPGA的DDS设计

5 DDS的FPGA实现

FPGA即现场可编程门阵列,它是作为专用集成电路领域中的一种半定制电路而出现的,既解决定制电路的不足,又克服原有可编程器件门电路有限的缺点。本设计采用Altera公司的Cvclone:II型器件。在实现DDS功能的同时,还能利用其中集成的Nios软核进行控制模块设计,加强集成度,减少器件使用和简化电路设计。

本设计的软件开发环境为Altera公司的Quartus II和Nios II IDE。

5.1 QuartusⅡ下的DDS设计仿真

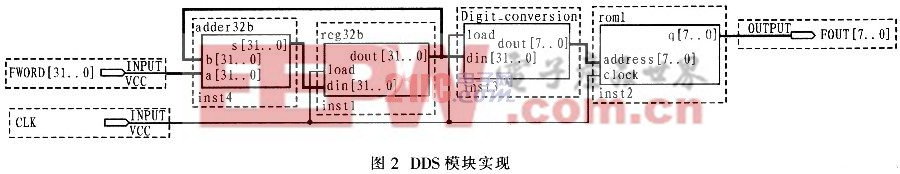

在Quartus II环境下利用VHDL语言对DDS内的寄存器、累加器及波形存储器进行设计及仿真,最后链接生成DDS模块,如图2所示。

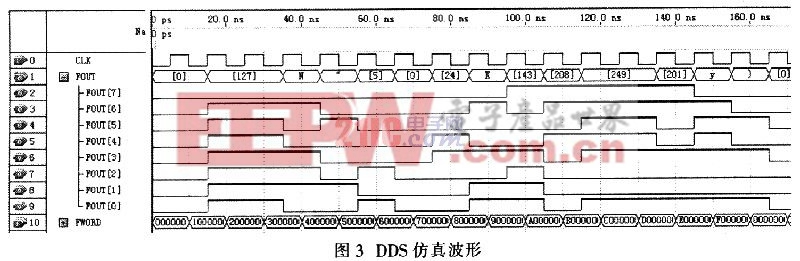

在检查编译文件后对DDS模块进行仿真,仿真图如图3所示。至此在FPGA内已成功建立DDS模块。根据所选用的具体器件内部存储量的不同,可以根据自身需要更改ROM有效地址位数和ROM存储波形的有效位数以提高系统的杂散抑制能力。

5.2软核的硬件定制和软件设计

利用Quartus II内的SOPC Builder工具完成Nios软核内的CPU、Memory、I/O口等所需硬件定制。同时在NiosⅡIDE环境下运用C语言完成软核内控制系统功能设计。

6 结束语

本文对直接数字频率合成器结构、工作原理及DDS杂散分析进行了较深入研究,并在理论研究的基础上结合Ahera公司的CycloneII器件完成了DDS的设计和实现。同时利用CyclonelI器件内的Nios软核将DDS与控制系统模块集成到一块FPGA器件内,简化设计难度,减小电路复杂程度。

评论