基于FPGA的Kalman滤波器的设计

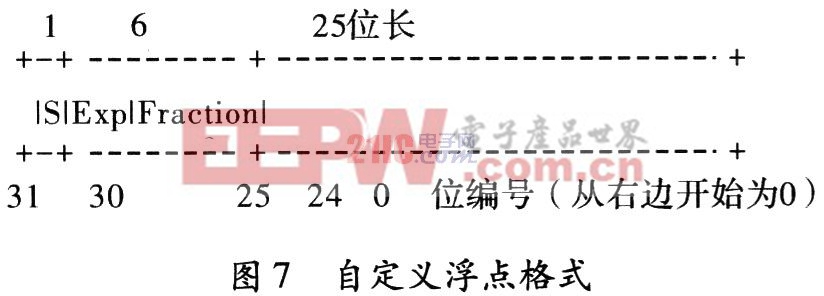

由于资源的限制,滤波中的运算过程只能以有限的精度进行,但过低的精度容易引起滤波发散,同时为了兼顾A/D高达24 bit的分辨率精度,在IEEE754单精度浮点数格式的基础上按照浮点表示的原则做了改造,将指数部分减少到6位,尾数增加到25位,25位尾数可以完全表示A/D输出的24位采样值,并削弱舍入误差的影响,其格式如图7所示。本文引用地址:https://www.eepw.com.cn/article/191740.htm

本系统对处理速度的要求并不高,运算部件的设计并不考虑速度优化。

加法器按以下通用的规则设计:

(1)阶码相减:两个操作数阶码相减,求得阶差d=|Ea-Eb|;

(2)尾数对齐:阶码小的操作数的尾数右移d位;

(3)尾数相加:完成移位处理后的尾数相加运算;

(4)转换:尾数相加的结果为负数时,转换为符号尾数的表示方式;

(5)前导0/1的判定:判定由于减法结果产生的左移位数,对于加法判定是否右移一位或不移,对前导0/1判定的结果进行编码以驱动规格化移位;

(6)规格化:规格化有效位并且根据移位的方向和位数修改最终的阶码Ef;

(7)舍入:根据IEEE标准判定最终结果的舍入,如果需要入,则最末有效位加1;如舍入引起溢出,则需要有效位右移1位,同时阶码Ef加1。

乘法器的设计相对简单,与加法器一样采用简单的设计规则:

(1)指数相加:完成两个操作数的指数相加运算;

(2)尾数调整:将尾数f调整为l/f的补码格式;

(3)尾数相乘:完成两个操作数的尾数相乘运算;

(4)规格化:根据尾数运算结果调整指数位,对尾数进行舍入截位操作,规格化输出结果。

采用Altera提供的IP核,除法器能完成IEEE754单精度除法运算。数据进入该除法器前需要将自定义的浮点格式的阶码扩展为8位加上95,尾数右移两位,转换为标准单精度浮点,计算结果再由标准单精度浮点的按相反的方法转换为自定义浮点。

文中硬件编程语言是用Verilog实现的。

4 实测结果分析与结论

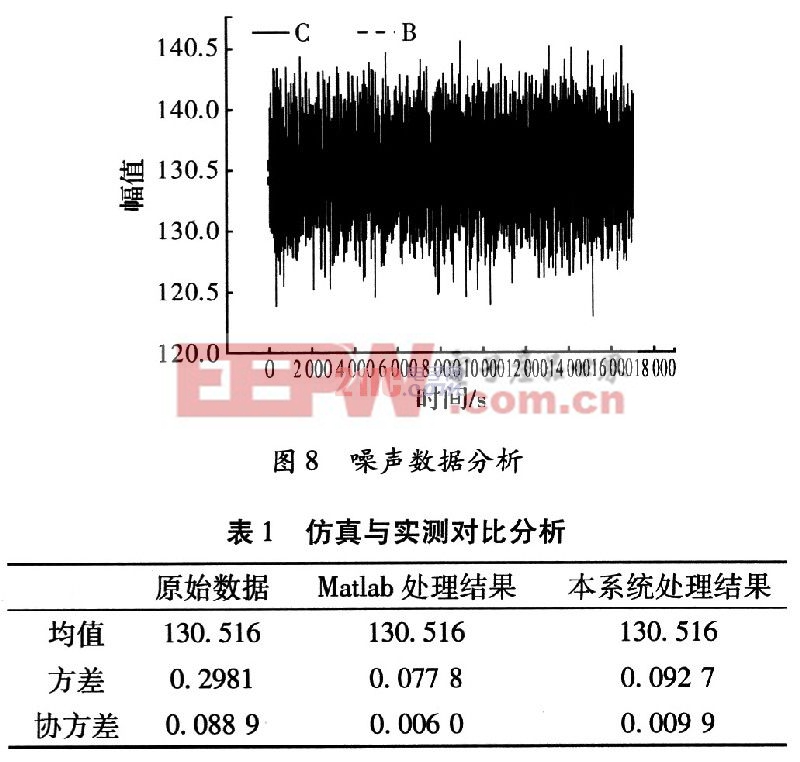

从系统输出数据中随机抽取一段数据用Matlab分析,其结果如图8所示。实线C表示的是滤波前的噪声:虚线B表示的是滤波后的噪声。很容易看出经过滤波后噪声降低了很多。仿真与实测对比分析如表1所示。

5 结束语

卡尔曼滤波器在很多领域具有重要的作用,可以实现数字信号处理功能,并能满足实时性的要求。用FPGA实现Kalman滤波过程,实现简便、成本较低、滤波效果好,被广泛应用于图像视频、陀螺惯导去噪、电子罗盘、雷达接收机目标跟踪处理、目标预测等图像、数据采集与处理领域。

评论