基于FPGA+DSP技术的Bayer格式图像预处理

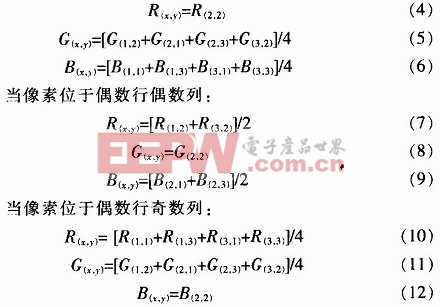

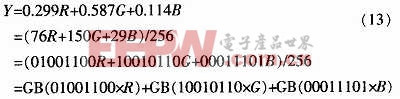

由于系统中TMS320DM642的视频端口使用的是8位RAW采集方式从CMOS传感器中采集图像,为了减轻DSP的运算负担,FPGA还需要将图像数据转换成Y亮度信号。将得到的RGB图像信号,通过浮点算法公式转换成亮度信号,具体推导公式如下(GB代表取高8位数据):

2.2 FPGA的硬件实现原理

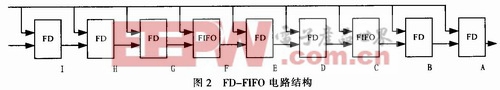

由于双线性插值法需要将图像数据采集成3x3的图像矩阵,系统采用一种由FPGA硬件元器件构成的FD-FIFO模型取图像矩阵。电路如图2所示。本文引用地址:https://www.eepw.com.cn/article/191433.htm

如图2所示,每个移位寄存器FD和先入先出寄存器FIFO左侧上端信号为时钟输入信号(上升沿有效),左侧下端信号为8位的像素信号。图像矩阵的采集流程为:8位的图像信号送到第1个FD,然后经过移位操作从第3个FD存入左边第1个FIFO,存入一行图像数据后,等第2行图像数据送达时,第2行的图像数据经过移位操作从FD存入左边第1个FIFO,同时存储在第1个FIFO的数据开始读出到第4个FD,再经过移位操作存入第2个FIFO,等待两行图像数据都存储后,当第3行图像数据送达至第3个FD,同时后面2个FIFO分别读出前两行的前3个图像数据时,就可以从FD和FIFO的输出端口读取到1个3x3的图像数据矩阵:3x3矩阵第1行从左到右的数据为ABC,第2行的数据从左到右为DEF,第3行的数据从左到右为GHI。

CMOS图像传感器采集的图像大小固定为2 592x1 946x12 bit的Bayer图像,FPGA先用一个12位输入8位输出的移位寄存器取图像的高8位,再利用FD-FIFO得到3x3的图像矩阵,然后可以根据双线性插值法计算图像的RGB信号。双线性插值法虽然算法简单,且易于实现,但是存在边界效应。系统对边界效应做了如下的处理方法:对图像四周全部补零,即先将图像扩展成2 594x1 946大小,然后计算得到2592x1 944大小的图像,这样得到的图像仍是完整尺寸。只需在运算的时候,针对不同四周特殊的像素采用裁减的公式(系统中不产生零像素,只是对计算公式中相应边界元素补零)。过程如下:

第1行图像读入第1个FIF0后,第2行图像开始读入左边第1个FD的时候,开始计算第1行RGB数据,这时候第2个FIFO没有数据,相当于在第1行的数据前面补零。第1 944行图像读入第1个FIFO后,第1 943行图像读入第2个FIFO的时候,开始计算最后1行(第1 944行),这时候第1个FD已经没有数据读入,相当于在第1 944行的数据后面补零。由于FD具有延时效应,所以在读写时,前1个FIFO开始读写时,再经过延时2个时钟周期,才到达后1个FIFO,所以相邻的FIFO读写使能信号要间隔2个时钟周期。

对列的操作也是如此,每一行的第1个元素读出到B、E、H位置时开始计算,这样每一列的第1个元素前相当于是零元素。每一行的最后一个元素读出到B,E,H位置时开始计算,这样每一列的最后一个元素后相当于是零元素。

评论