视频图像灰度信号直方图均衡的FPGA实现

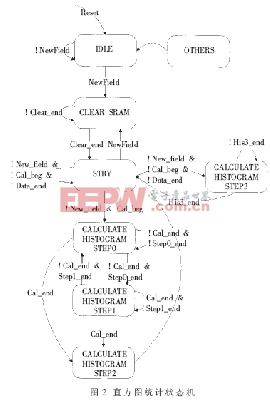

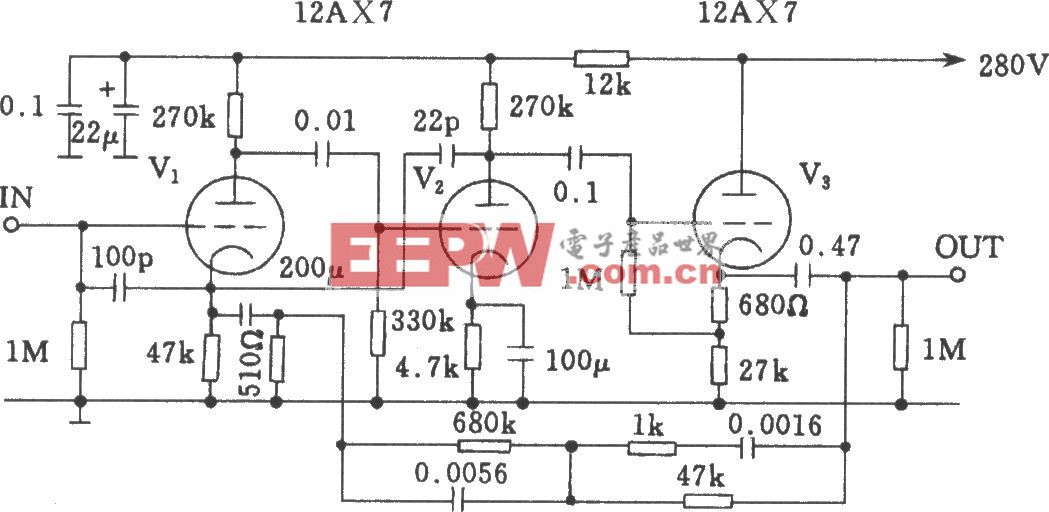

每当一个新的图像数据进入统计模块,就将SRAM内相应地址的统计数据读出,累加后再存入该地址。由于前后数据可能是一样的,会造成对同一个SRAM地址同时读写而引起错误。这就需要一个模块对整个过程加以控制。基本的思路是:对前后数据进行比较,若前后数据相等就将计数器累加,直到发现数据不等才将统计数据写入SRAM,这样就从根本上避免了读写同一个地址的可能性。直方图统计状态机实现框图如图2所示。

由于使用了乒乓模式(一块SRAM用于当前场的统计,另一块用于前一场灰度均衡的计算),状态机在上电复位后首先需要将用于统计的SRAM清空,这可以利用视频的场消隐时间加以处理(相应的状态机状态是CLEAR SRAM状态),然后等待有效数据进入(对应于STBY状态),一旦有效灰度数据进入,状态机就进入统计状态0(CALCULATION HISTOGRAM STEP0)。此时,首先读出SRAM相应于该灰度值的数据,同时将数据延迟并观察前后数据是否相同,如相同则继续停留在该状态,将计数器加1;否则进入统计状态1(CALCULATION HISTOGRAM STEP1)。进入状态1后,计算上一个灰度值的统计数据(将从SRAM中读出的值加上计数器的值再加1)存入SRAM,同时还要读出SRAM里相应于当前灰度值的数据。此后的工作与状态0相似。以此类推,状态不断在状态0和状态1之间切换,直到有效数据结束后进入统计状态2(CALCULATION HISTOGRAM STEP2),状态2 的作用是将这一行的最后一个灰度数据的统计信息写入SRAM。随后回到STBY状态,等待下一行数据。当所有有效行都统计完后,进入状态机的统计状态3(CALCULATION HISTOGRAM STEP3),重新将灰度统计数据累计后存入SRAM。

4 SDRAM 控制器的实现结构

输入输出视频图像的速度(13.5MHz)远低于SDRAM的最高速度(143MHz),假如以单个数据对SDRAM读写(Single Write/Single Read),根本无法发挥SDRAM高速的优势,所以必须使用SDRAM的突发模式(BURST MODE),即一次读出或者写入多个数据。以美光公司(MICRON)MT48LC1M16A1S SDRAM为例,它支持1、2、4、8个字或者整页(256个字)的读写。由于属于两个时钟域,所以必须对写入或者读出SDRAM的数据缓存。在这里,读写模块分别使用两个深度为64、宽度为16bit的双口SRAM以乒乓的方式加以实现。一次突发模式读写的数据量都是64个字,因此选择深度为64的SRAM是一种折衷的办法,数据过少无法发挥突发模式的优势,数据过大则需要更多的SRAM作为缓存,使开销过高。实践证明一次读写64个数据比较合适。

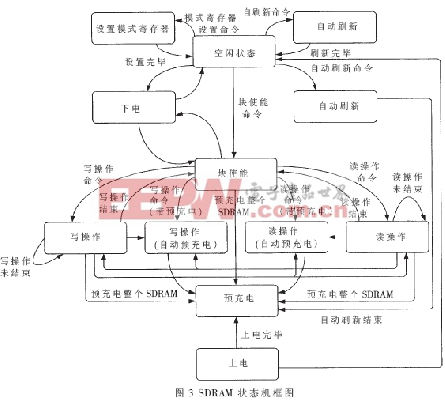

由于SDRAM结构的特殊性,它的读写刷新操作需要满足一定的时序要求,所以需要专门的控制器来维护对SDRAM的操作。图3是Hynix Electronics公司HY5DV641622AT 的SDRAM的状态机框图,该框图包含SDRAM上电时序、模式寄存器的设置、读写控制、预充电和定时刷新等多个环节。控制器的具体实现可以参考Xillinx或者Altera公司相关文档和各家DRAM厂商的资料。

评论