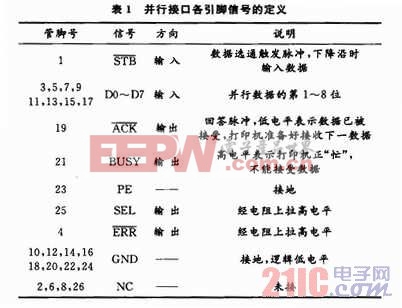

微型打印机与FPGA的硬件接口及软件设计

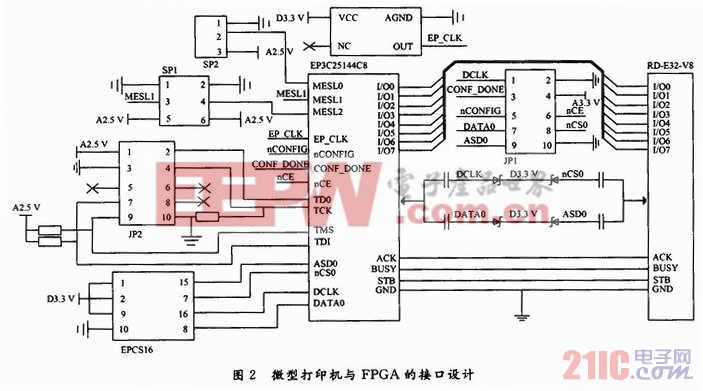

设计控制功能模块时,由于FPGA有富余的I/O接口,所以打印机可以不经过另外的接口电路而直接与FPGA相连接,同时FPGA其内部的嵌入式阵列块 EAB是输入端口和输出端口都带有触发器的RAM块,可实现小容量的ROM和RAM,无需外部扩展ROM和RAM,也无需外加锁存器。FPGA芯片可以通过编程配置其内部逻辑单元,通过编写软件来设计微型打印机控制器,所以只需分配好与打印机相连接的I/O接口,读写相连的信号线即可。打印机的BUSY,和D0~D7信号接口分别由FPGA在编程综合过程中分配通用I/O接口,接口方式如图2所示。

本文引用地址:https://www.eepw.com.cn/article/191405.htm

本文引用地址:https://www.eepw.com.cn/article/191405.htm

图中JP1和JP2是FPGA的配置接口,JP1与EPCS16SI16N外部存储芯片一起,构成FPGA的串行(AS)配置端口,当程序调试完成后,可将程序经JP2口下载至配置芯片EPCS16SI16N,FPGA上电之后,系统自动将配置芯片中的程序读入FPGA内,完成逻辑功能块的配置。JP1是 JTAG配置口,主要作用是方便程序的现场调试,不需经过外部存储器,程序直接下载到FPGA中完成逻辑功能块的配置,以验证程序设计能否实现预期的功能。SP1与SP2用以设置配置芯片与FPGA数据传输的工作方式,例如MESL2,MESL1,MESL0为“010”时,配置为标准串行端口,配置电压为3.3 V;若为“100”时为快速串行配置端口,配置电压可在3.3 V和2.5V两者中选其一。P1是有源晶振,可提供FPGA系统时钟频率。RP1是打印机数据端口的上拉排阻,这样输出数据与端口数据逻辑与之后输入打印机,避免显示乱码。打印机RD-E32-V8与FPGA由8根数据线和3条控制、状态读写线连接,另有一条线将2部分的接地端连接到公共的模拟地线。

2 软件实现

系统软件设计是基于VHDL语言编写的。软件设计的关键是在打印机工作时序的基础上完成微型打印机与FPGA之间数据和指令的读写和状态的检测。

2.1 控制时序与原理

控制过程的时序在延迟时间上有严格的要求,所以,设计控制程序时,必须考虑打印机状态转换和数据传输的延迟时间。当数据线上有待打印的数据时,打印机并不是立即将数据打印输出,必须根据当前的打印机状态来判断。

当BUSY状态被检测到为“1”时,说明打印机处于“忙”状态,此时打印机不会接收任何数据。当BUSY信号为“O”时,说明打印机处于“空闲”状态,先向数据线写入数据,在延时时间符合时序的情况下,通过FPGA控制信号,将数据写入打印机。为数据选通触发脉冲,下降沿时输入数据,对低电平的时间时序上也有要求,最小为O.5μs。当下降沿到来的同时,数据即送入打印机,同时BUSY信号由低电平跳变为高电平,阻止FPGA向打印机数据线写入数据。当数据输入以后,直到回答脉冲跳变成低电平,此时表示数据已被接受,而且打印机准备好接受下一数据,之后大约5μs时间以后,BUSY信号变为低电平,之后约5μs信号变高。对打印机的控制是通过查询方式实现的,根据打印机工作时序,将打印机控制过程分为3个状态,打印机控制程序基于这3个状态,采用VHDL语言的有限状态机编写实现。时序与状态转换如图3所示。

评论