基于FPGA的数字示波器

2.4.2 FIFO及触发电路设计

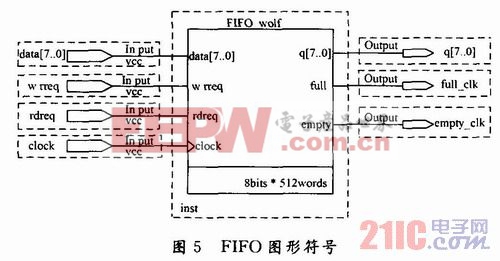

该系统利用FPGA设计大小为1 024 B的FIFO,实现对A/D采集数据的快速存储。A/D采集电路开启时,FIFO开始存储数据。利用FPGA设计的FIFO如图5所示。本文引用地址:https://www.eepw.com.cn/article/191331.htm

当FIFO所存储的数据在屏幕上还原出波形时,选取一个固定的起始点,使后面的波形能够连续且没有重叠的在屏幕上显示。这个起始点反映到系统中就是触发信号。该系统中采用内部软件触发方式,通过软件设置触发电平。所设置的施密特触发器参数易于修改,从而抑制比较器产生的毛刺。当采样值大于触发电平,则产生一次触发。该方式充分利用了FPGA的资源,减少外围电路,消除硬件毛刺产生的干扰,易于调整触发电压。

2.4.3 SoPC系统设计

由于采集的数字信号需要进行高速处理,因此本设计利用了FPGA,高效的SoPC,对FIFO(数据缓存)中的数据进行处理,并控制TFT液晶显示所采集信号的波形。

3 系统软件设计

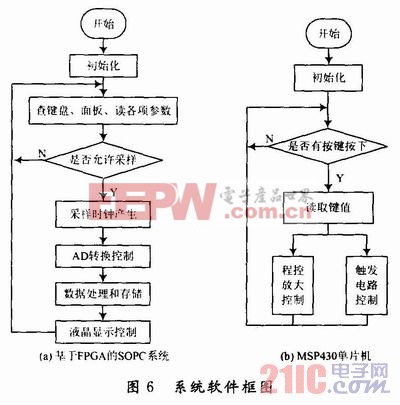

系统软件设计实现了人机交互、信息提示、系统启动与复位等功能。系统软件设计如图6所示,该系统包含采样时钟产生单元、显存控制单元、TFT液晶显示和可编程放大控制等模块。Verilog可以形成原理图,对其进行仿真实现,而且SoPC配置的软核CPU允许挂接这些单元,很容易实现总体功能的合理规划。

评论