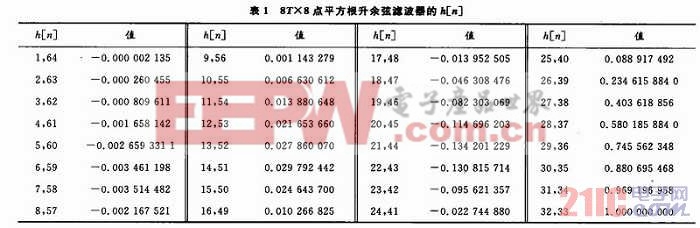

根升余弦脉冲成形滤波器FPGA实现

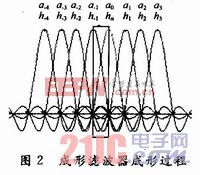

设发送端传递的二进制数据是{…,a-4,a-3,a-2,a-1,a0,a1,a2,a3,a4,a5,…},则发送滤波器的输出如图2所示,该波形函数可表示为:

![]()

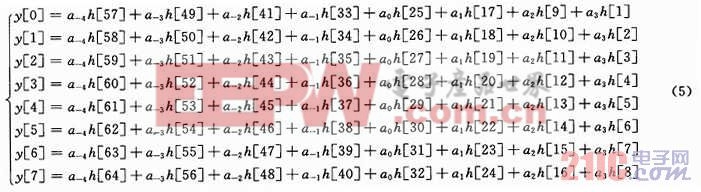

可以看出,当前传递信息{a0}时刻对应的波形信号的上升沿y[1..8]分别由h-4[57..64],h-3[49..56],h-2[41..48],h-1[33..40],h0[25..32], h1[17..24],h2[9..16]与h3[1..8]线性表示,如式(5)所示:

2 二进制基带信号平方根升余弦成形滤波器的FPGA实现

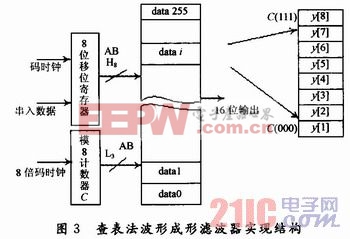

在分析文献的基础上,文中波形成形滤波器的实现采用的查表法结构如图3所示。其中,ROM单元存储待成形的数据与成形滤波器的冲击响应的卷积结果。模8计数器的工作时钟速率是待成形数据速率的8倍。待成形数据从8位移位寄存器的低位移入后,选择ROM表中的数据块da-ta i,同时模8计数器C从(000)2~(111)2计数,并用该计数结果C(j)选择输出data i中的y[j]。当计数器C计数归零时,新的待成形数据从低位移入8位移位寄存器。该设计的一个优点是:ROM表中的数据在计算时,ai可采用双极性码,而查找表地址产生电路使用单极性码。文中设计时,波形数据的计算采用了反逻辑、双极性、不归零码,即输入信息符号序列{0,1)映射为{+1,-1),持续时间不变。

电气符号相关文章:电气符号大全

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

脉冲点火器相关文章:脉冲点火器原理 数字滤波器相关文章:数字滤波器原理

评论