基于FPGA的部分响应CPM信号解调器的设计

(2)加比选ACS 模块

此模块分为两部分:①计算路径度量值;②选择当前时刻最佳路径。当前状态的路径度量值为该状态下所有可能的路径度量值中的最大值。最佳路径为最大路径度量值对应的上一状态。在设计中采用确定CPM 调制的起始状态的方法。

复位时将起始状态的路径度量值赋值为0;将其他状态的路径度量值赋值为一个较小的负数。采用这种方式有效避免解调时起始状态的不确定性。

CPM 的解调在一定的译码数量后,路径度量值的存储器便会饱和溢出。该设计采用一种简单方法防止溢出:每次路径度量值计算完成后,判断其最大值,如果最大值超过某一确定的正值,则所有的路径度量值减去一个正值。再判断是否有度量值小于一个确定的负数,如果有,则将其值重新赋值为一个较小的负数。仿真中,证明了这种方法的可行性。

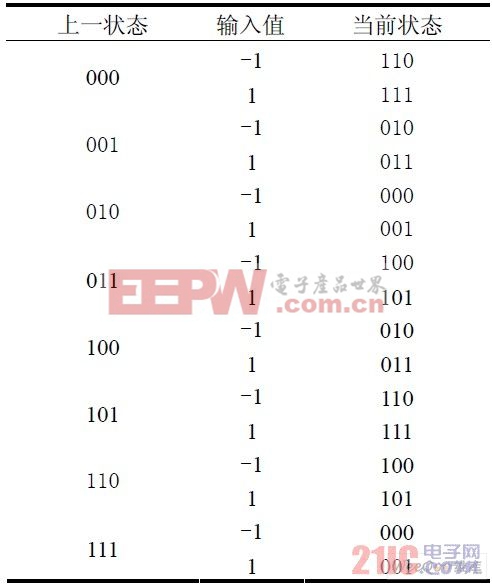

表1 输入数据与状态间转移关系

(3)回溯模块

此模块包括幸存路径存储和判决输出。在模块中比较当前时刻各状态的路径度量值,求得最大路径度量值,以及对应的当前状态。从表1 可知,状态的最低位可以表现上一时刻的输入值,最低位为0 时,表示上一时刻的输入码字为-1;最低位为1 时表示上一时刻的输入码字为1。

3 硬件实现、时序仿真和性能

这里选择的FPGA 是Xilinx 公司的Virtex5 系列的XC5VSX95T 芯片,设计软件为ISE, Synplify, Modelsim,Matlab,设计语言采用VHDL 硬件描述语言。

评论