基于FPGA的高精度信号源的设计

2)2-ASK、2-FSK、2-PSK数字调制信号 要产生2-ASK、2-FSK、2-PSK等数字调制信号比较容易。只需将数字基带信号在其传输时钟信号的作用下,逐位输入模块,用基带数字信号的‘1’和‘0’来选择不同幅度、频率或相位的正弦信号输出即可。

2-ASK信号:用3.125 MHz的信号表示数字信号的‘1’,用输出幅度为0表示数字信号的‘0’。

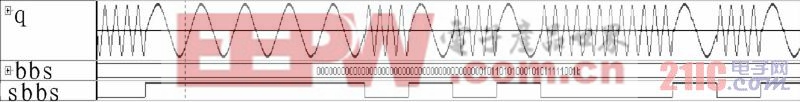

2-FSK信号:用3.125 MHz的信号表示数字信号的‘0’,用582.077 kHz的信号表示数字信号的‘1’,如图3所示。

图3 2-FSK信号字调制信号

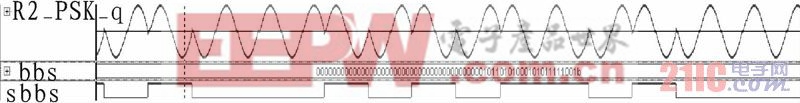

2-PSK信号:用初始相位为0的正弦信号的‘1’,用初始相位为180°的信号表示数字信号的‘0’。如图4所示。

图4 2-PSK信号字调制信号

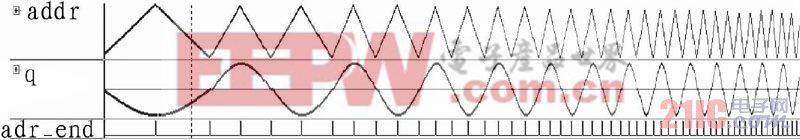

3)扫频功能 扫频功能的实现是通过改变步进来实现的。每产生一个周期的正弦信号以后,将步进递加,为便于观测,设计中设置S初始值为(50 000 000)10,步进递增幅度为(10000000)10,实现了扫频功能,扫频起始频率为582.077 kHz。扫频步进约11*15 kHz,扫频信号如图5所示,同时可以提供各频率信号的同步信息。只要改变步进初始值及递增幅度即可完成更宽扫频范围及扫频步进更佳的扫频信号。事实上,FM信号也可以通过对输出信号的步进的控制来加以实现。

图5 扫频信号

5 硬件电路的实现

设计的最终目的是为了用硬件实现电路,因此,还要设计输入步进设置及模式选择的键盘模块、频率设置数据显示模块等VHDL程序模块;后级的低通滤波网络,功率放大电路等等。完成这些工作,即可完成一个完整的DDFS信号源的设计与制作。

6 结束语

本文的创新点为对DDFS设计进行优化,充分利用Cyclone II系列FPGA的片上资源,产生了最高频率可达9.312 5 MHz.最低频率分量及频率分辨率低至MHz量级的正弦信号。通过进一步优化DDFS各模块的性能,如减少相位累加器、数据取补码等模块的运算时间,进一步提高系统工作的最高频率;进一步优化后级滤波网络的特性等,就可以获得性能曲线更平滑,输出频率更高,带负载能力更强的优质的信号源。同时还可以增加FFT算法模块,对信号进行频谱分析等其他功能。

评论