基于FPGA的高效FIR滤波器设计与实现

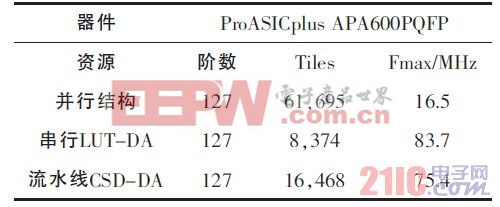

表2所列是不同结构滤波器的综合结果。其中并行结构是最差的一种结构, 它占用资源多、速度慢; 串行LUT-DA结构, 虽然占用资源少,最大工作频率高, 但毕竟是串行结构, 不能在一个时钟节拍完成对一个采样点的滤波运算; 而流水线CSD-DA结构则无论在速度, 还是面积上,都具有比较明显的优势。如果工作时钟为75MHz, 那么, 一个时钟节拍便可以完成一次输出, 处理330个采样点的单通道信号仅需4.4μs,可以满足测井实时性要求。

表2 滤波器的综合结果

4 结果分析

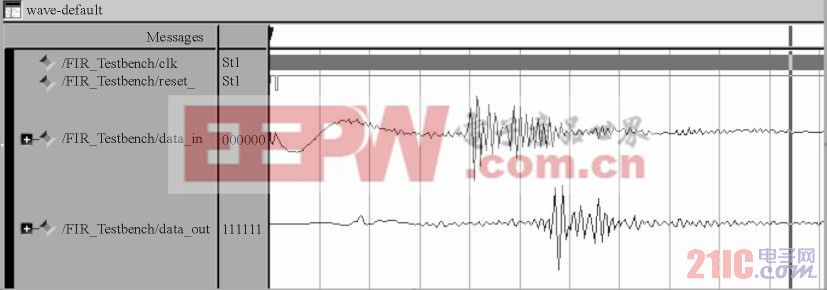

为了验证滤波器的功能是否正确, 可对本设计在Modelsim中进行仿真。若原始波形为带噪声的声波信号, 那么, 其滤波的结果如图4所示。

图4 滤波器在Modelsim中的仿真结果

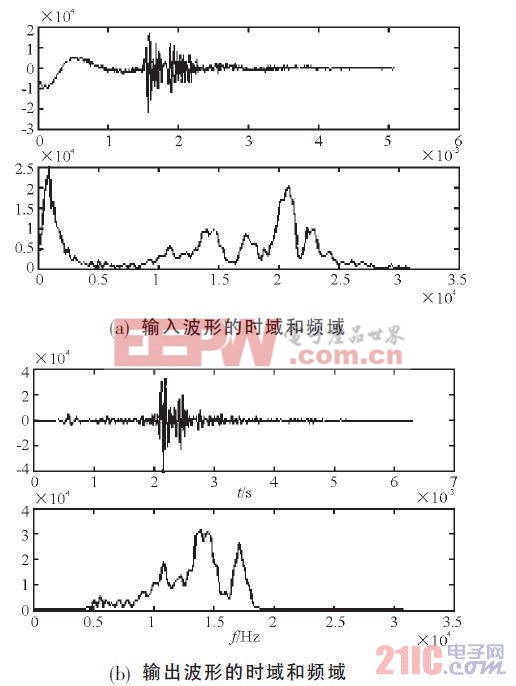

图5所示是滤波器在Matlab中的仿真结果, 可以看出, Modelsim和Matlab的仿真结果一致。在频域上, 对比图5 (a) 和图5 (b) 可以看到, 其滤波后的波形只保留了5kHz~18kHz的频谱部分, 这说明流水线CSD-DA结构的数字滤波器设计正确。

图5 滤波器在Matlab中的仿真结果

5 结束语

本文详细讲述了通过Matlab工具设计FIR线性相位滤波器的方法, 并针对声波信号设计了优于传统结构的流水线CSD-DA结构, 该结构具有较明显的速度和面积优势。文中也通过仿真实验证实了设计的合理性和正确性。但值得指出的是, 该结构只适合固定滤波器系数的场合, 而如果要进行修改, 则需要重新对系数进行CSD编码和流水线分割。

评论