多通道频率检测技术的FPGA实现

3.2 系数存储模块

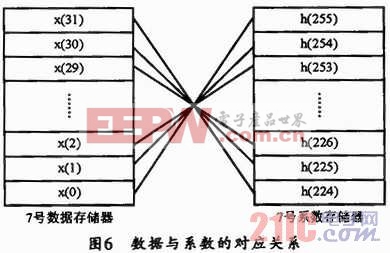

对于256阶原型低通滤波器,可以将h(0),h(1),…,h(255)这256个系数分成八组,每组32个,分别存储到八个存储器当中,存储器0存储的系数为:h(0),h(1),…,h(31);存储器1存储的系数为:h(32),h(33),…,h(63);以此类推。存储器可使用逻辑(LUT)实现,也可使用专用存储模块Block RAM来实现。FIFO中的目标数据和存储器中系数做乘法运算时,两者的对应关系如图6所示(以7号存储器为例)。本文引用地址:https://www.eepw.com.cn/article/191272.htm

当8个数据存储器的最后一个单元数据被读出时,8个系数存储器的0号地址单元的系数也将同时被读出,然后分别作乘累加,最后作为y(0)输出。同理,当8个数据存储器的第二个数据被读出时,8个系数存储器的1号地址单元的系数也同时被读出,然后分别作乘累加,最后的结果作为y(1)输出,以此类推,得出全部y(2)~y(31)的输出。最后将y(0)~y(31)作为FFT的输入数据进行32点FFT运算。

3.3 FFT的实现

设计中的FFT变换可通过调用Xilinx的IP核来实现。FFT采用流水型结构,该结构能够对连续数据流进行处理,只是结果上有若干周期的延迟。FFT核的输入输出的引脚关系如图7所示。

3.4 仿真结果

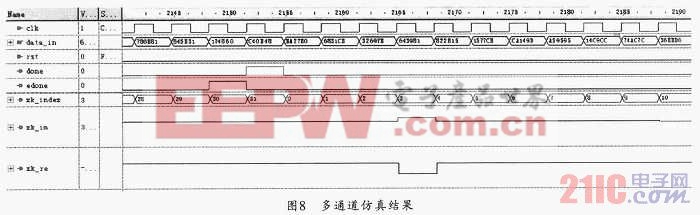

FPGA的设计软件可采用ALDEC公司的Active_HDL8.2,并可用Testbench文件对所设计模块进行仿真。Testbench文件读取时,可由Matlab

产生的信号数据作为FPGA仿真的激励信号,信号形式采用28.1MHz的单频信号:

将信号数据送入图4所构建的系统后,即可在ALDEC下得到图8所示的仿真波形。

由图8可以看到,该仿真结果在第3号通道上有信号输出,这与图3中用Matlab仿真的结果一致,从而验证该模块设计的正确性。

4 结束语

本文针对多信道频率检测技术进行了研究,并在传统检测方法的基础上,结合FPGA的特点,构建了一种基于DFT多相滤波器组信道化的高效结构。该结构可解决频率截获概率与频率分辨力的矛盾,同时也为实现全概率频率捕获提供一种参考方案。经过仿真及测试验证,该方案能满足检测指标要求,从而为多信道频率检测技术提供一种设计参考。

评论