基于FPGA的出租车计费系统设计

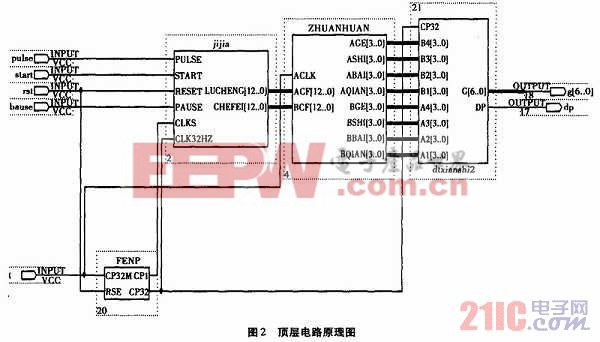

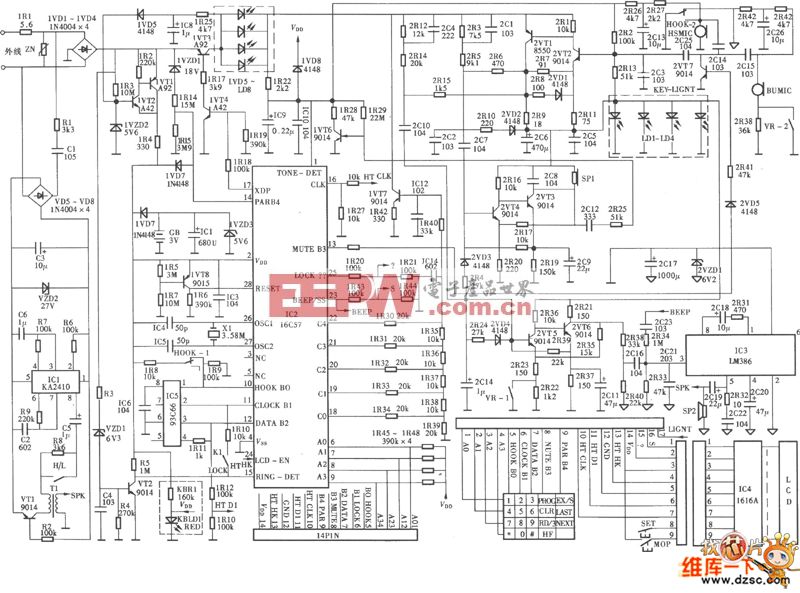

3.5 整体电路

将各个模块按照输入输出关系连接,顶层电路原理图如图2所示。g[6…0]为七段显示码输出,通过动态扫描依次控制8个数码管的显示,dp为小数点位。本文引用地址:https://www.eepw.com.cn/article/191094.htm

4 系统仿真验证

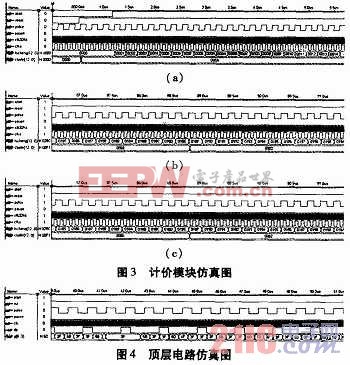

用MAX+plusⅡ软件对各个子模块及顶层原理图进行了时序仿真,仿真波形如图3所示。

控制计价模块仿真图如图3所示。由图3(a)可得,当reset=1,start=1,且pause=0时,表示出租车处于行驶状态,此时路程开始递增,当不超过3 km时,车费为5A即90,起步价9.0元。由图3(b)可得,当超过3 km后,车费每行驶1 km加20(即2元)。由图3(c)可得,当reset= 1,start=1,且pause=1时,出租车处于等待状态,此时路程不再递增,而时间递增,当时间达到3分钟时,车费加5(即0.5元)。

顶层电路的仿真图如图4所示。从图中可以看出,随着输入的变化,从g[6…0]输出了共阴的数码管显示编码,dp也在对应的数码管处,输出高电平点亮小数点。

综上分析,本设计的软件仿真结果正确,与设计要求相符。

评论