基于FPGA的汉明距离电路的实现

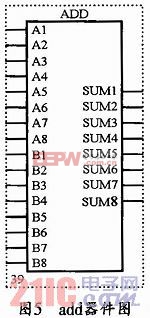

1.4 汉明加法器

图5所示是一个汉明加法器的add器件图。add通常是采用求和网络法求和。求和网络法将ROM输出的数据两两通过一个加法器相加后,可将得出的结果再两两通过一个加法器相加,依次将各项计算结果相加在一起,其最终的累加结果便是汉明距离。本文引用地址:https://www.eepw.com.cn/article/191076.htm

2 汉明电路的仿真调试

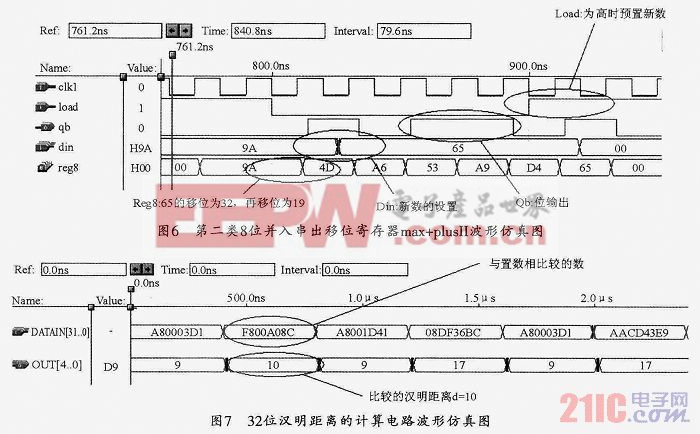

2.1 8位并入串出移位寄存器的max+pluslI仿真

8位并入串出移位寄存器max+plusII波形仿真如图6所示。其中的Clk为移位时钟信号;Load为并行数据预置使能信号;Din是8位二进制并行预置数据端口;Qb表示当前值reg(0)向qb输出;Reg(8)为当前值和移位值(如:9A 1001 1010B;移位后:4D 0100 1101 B:第二次移位:A6 10100110 B)。

2.2 32位序列汉明距离电路的实现仿真

选取查找表-求和网络法来实现32位汉明距离的计算时,可分别将(D6~D14)、 (D15~D23)、(D24~D32)作为查找表的地址线,再由此计算出序列D6~D32的汉明距离。而其序列D0~D5的汉明距离可以采用逻辑函数获得,具体的波形仿真如图7所示。

图7中,Datain[31..0]为汉明距离电路的输入端口;Out[4..0]为汉明距离计算输出端口(内置的32位数可用十六进制表示为000000 00)。例如F800A08C即1111 1000 0000 0000 1010 0000 10001100B,输出的汉明距离d为10。

3 结束语

设计完成后,可使用FPGA(即现场可编程门阵列)进行下载验证,FPGA是专用集成电路(ASIC)领域中的一种半定制电路,FPGA既可解决定制电路的不足,又可克服原有可编程器件门电路数有限的缺点。而使用Max+PlusⅡ软件和VHDL语言进行电路设计,不仅可以进行逻辑仿真,还可以进行时序仿真。由于本设计在编写过程中使用了较多的与门和异或门,所以,在波形仿真图中,波形显示具有比较长的延时。但是,自行编写的计数器功能完善,程序简单明了,完全可以实现32位汉明距离的计算。

DIY机械键盘相关社区:机械键盘DIY

评论