基于89C55和FPGA的频率特性测试仪

2 理论分析与计算

2.1 DDS原理分析

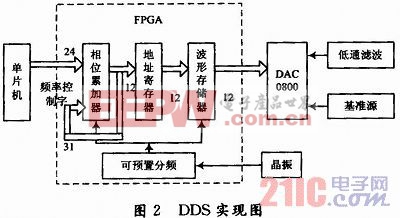

DDS是一种应用数字技术产生信号波形的方法,主要组成:相位累加器、波形存储器、D/A转换器和低通滤波器。基本工作原理是:在参考时钟信号的控制下,通过由频率控制字K控制的相位累加器输出相位码,将存储于波形存储器中的波形量化采样数据值按一定的规律读出,经D/A转换和低通滤波后输出波形。其FPGA内部实现框图如图2所示。本文引用地址:https://www.eepw.com.cn/article/191062.htm

通过DDS技术实现频率合成前需要确定DDS的主要性能参数:

设参考频率源频率为fclk,采用计数容量为2N的相位累加器(N为相位累加器的位数),频率控制字为M,则DDS系统输出信号的频率为fout=fclk/2N×M,频率分辨率为△f=fclk/2N。若选取晶振频率为40 MHz,频率控制字为24位,相位累加器的位数为31位,此时的DDS模块逻辑框图如图3所示,这样的理论输出频率范围为0.02 Hz~312 kHz,步进约为0.02 Hz(40 MHz/231)。

2.2 双T网络

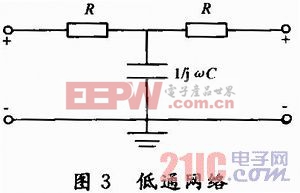

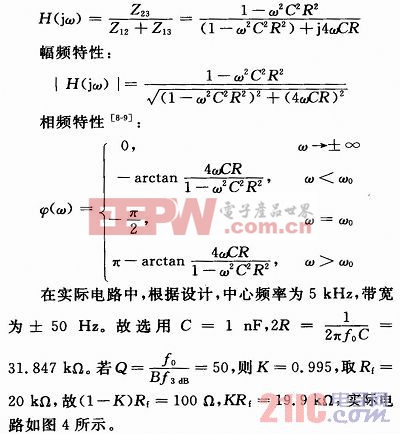

双T网络可看作由一个T型低通网络和一个T型高通网络组成。低通网络如图3所示。将其中的电阻、电容全转换成阻抗表示。传递函数H(jω)为:

评论