基于FPGA高速数据采集与传输的声幅测井系统

3 系统软件设计

设计的数据采集系统是基于高性能FPGA芯片实现的,FPGA承担了绝大部分的控制和数据处理任务,是设计的核心内容,对FPGA进行模块化设计,是大型系统设计的常用方法。本项目中将FPGA分成USB控制模块、采样控制模块、触发脉冲产生模块和RAM等几个主要功能模块来设计。

FPGA模块的原理如图3所示。其工作原理为触发脉冲产生模块,根据设定的参数周期性输出脉冲信号触发采样控制模块对A/D进行采样。采样控制模块在接收到USB控制模块的启动信号后,只要接收到触发信号就开始采样数据,并判断采样数据是否满足要求,如果满足要求则把数据存放于RAM中,且在采样结束后触发USB控制模块上传数据。本文引用地址:https://www.eepw.com.cn/article/190675.htm

通电后,先对USB芯片初始化,然后如果接收到采样结束信号或上传结束信号并且RAM在还剩余有数据的条件下把RAM数据上传,若接收到下传信号,则把计算机下传的数据按要求分配到各端口。

3.1 采样控制模块

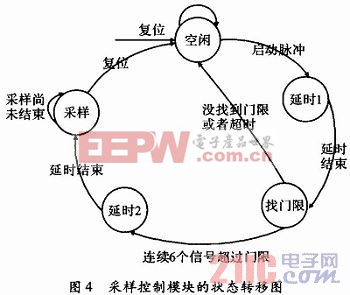

采样控制模块根据外部触发信号,利用状态机对A/D的采样行为进行控制。共有5个状态,每个状态的动作在代码中进行了详细描述。

第1个状态:空闲状态(IDLE),表示程序无任何操作,在等待外部触发信号的到来。

第2个状态:延时1(第一个等待状态,WAIT1),表示收到触发信号后需要禁闭A/D一段预先设定的时间,这段时间不进行任何操作。

第3个状态:找门限(门限判决状态,THDET),在规定的时间段时间里判断A/D采样的信号中是否有连续6个采样大于门限的值,如果有,等待一段时间后把采样后的数据存入缓冲区以便上传给上位机。否则继续等待下一个触发信号。

第4个状态:延时2(第二个等待状态,WAIT2),表示已经满足采样要求后再禁闭A/D一段预先设定的时间,这段时间不进行任何操作。然后启动A/D进行采样。

第5个状态:采样状态(SAMPER),启动A/D进行采样,并存储数据。

此处为米莉(Mealy)型状态机,Mealy型状态机的输出不仅与现态有关,而且和输入也有关。

该状态机采取3段式描述方式:即使用3个always块,第1个always块采用同步时序描述状态转移;第2个always块采用组合逻辑判断状态转移条件,描述状态转移规律;第3个always块描述状态输出。

状态机的编码使用独热码(One-hot)编码,独热码编码的最大优势在于状态比较时仅需要比较一个位,从而一定程度上简化了比较逻辑,减少了毛刺产生的概率。

评论