基于FPGA的真彩VGA显示的实现

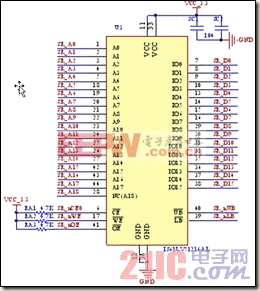

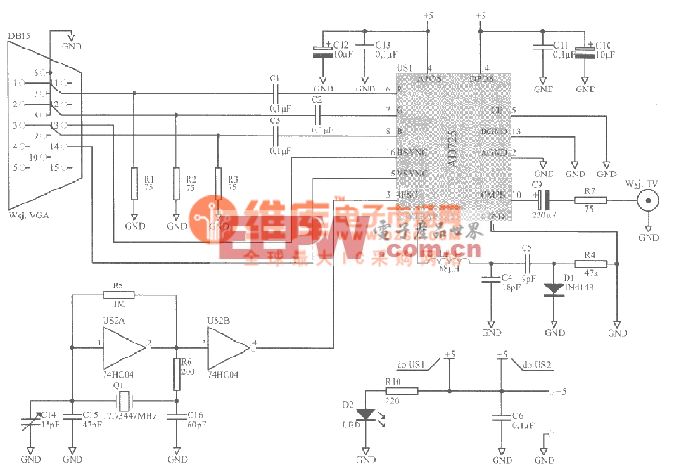

(3)SRAM:VGA刷屏数据显存IC,此处采用了ISSI的IS61LV51216AL-10TI 作为高速显存芯片。

2. 软件设计

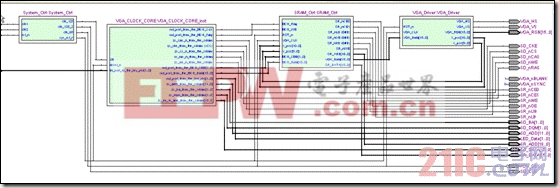

如上图所示,Bingo设计的真彩图像显示的工程的RTL图。

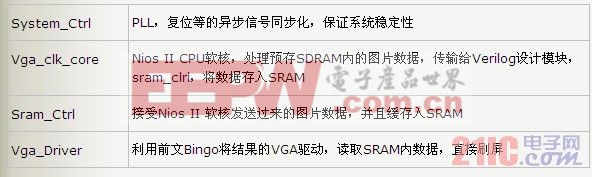

这应该算是真彩显示的最简单的设计吧,将图像数据随Nios II配置JTAG下载SDRAM,再读取专一值SRAM,刷屏实现真彩图像的VGA显示。本工程的软件架构如下,主要用了以下这几个模块:

3. 注意问题

关于CPU传输数据给Sram_Ctrl模块,Bingo采用了模拟6800总线协议,来对数据进行交换处理。当然若有更好的方案,您可以自行设计协议,Verilog相当的灵活。

关于时钟的处理,由于设计中设计到了大量数据的传输,时序上需要严谨,因此要严格处理好CPU与Verilog的跨时钟、VGA刷屏时钟、复位信号等的协调,以及稳态亚稳态,甚至时序约束。

评论