YUV分离的两种FPGA实现

工作流程如下:首先对双口RAM0进行写操作,写操作完成后经过316个CLK,开始对双口RAM1进行写操作。对双口RAM0进行读操作时,因为读操作只用到704个CLK,而写操作需要1 408个CLK,当对双口RAM0读完时,还需继续对双口RAM1进行写操作,等到双口RAM1输出ramfull高电平时进入下一个缓冲周期,此时对双口RAM0进行写操作,对双口RAM1进行读操作,如此循环,则实现了视频处理的流水操作。完成第一行数据的YUV分离输出所需要的1 408+316+704个CLK后,各行数据的输出则只需要1 408+316个CLK。于此同时基于速度的实现方式从提高系统工作时所能达到的最高时钟频率为出发点,利用了流水线的设计,提供了系统的频率,如果系统的工作频率是100 MHz,那么实际输出YUV分离视频数据所需要的时间仅为(1 408+316)×10-8。模块仿真如图6所示。本文引用地址:https://www.eepw.com.cn/article/190540.htm

4 性能分析

4.1 操作时间

前面已经叙述过基于面积实现方式,完成一行视频数据的YUV分离输出需要1 408+704个CLK,而由于需要充分利用行消隐期来完成数据的分离输出,因此FPGA与SDRAM之间的频率必须满足一定的差异,这就使得该方式不能获得较高的系统最高工作频率。假设FPGA的工作频率为48 MHz,SDRAM的工作频率为100 MHz,那么实际完成一行视频数据的分离传输需要的时间为1 408×10-8+704×(1/48 000 000),而基于速度的实现方式,由于采用了两片双口RAM,因此可以在同一缓冲周期分别进行读/写操作,而下一缓冲周期两片双口RAM的操作方式切换,进而完成了数据的无缝缓存与处理,利用流水线的方式使YUV分离数据的输出速度得到了很大的提高,并且使得该模块的系统最高工作频率得到了很大的提高。完成一行视频数据的分离输出需要的CLK个数为1 408+316+704个。假设该模块的工作频率为100 MHz,那么实际完成一行分离数据输出所需的时间为(1 408+316+704)×10-8,通过对比可以发现,基于速度的实现使得系统可以在较高工作频率下运行,利用流水操作,进而实现了速度上的提升。

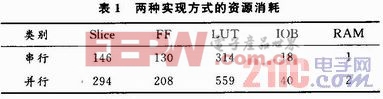

4.2 硬件资源

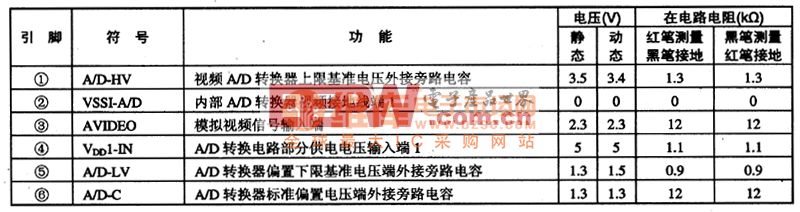

由上述可知,基于面积的实现方式只用到了一片双口RAM,而基于速度的实现方式用到了两片双口RAM,且用到了一个二选一多路选择器,同时后者的控制信号明显多于前者,不仅增加了寄存器开销,同时也增加了输入/输出端口的数量。通过对比可以发现,前者在面积上比后者确实有了较大优势。表1为2种实现方式的资源消耗列表。

5 结语

本文提出了YUV分离的两种FPGA实现方法,基于面积的实现利用了一片双口RAM,而基于速度的实现方式利用了两片双口RAM。通过对比发现,前者在消耗资源上获得了较大的改进,对整个系统的集成化有重大作用;而后者采用了两片双端口RAM的乒乓操作流水,实现了视频数据的输出,对提高整个系统的实时性意义重大。无论从面积还是速度为出发点,二种方案对整个系统性能的提高都意义重大。

电子镇流器相关文章:电子镇流器工作原理

评论