基于FPGA的串行外围接口SPI设计与实现

3 设计的仿真、综合与实现

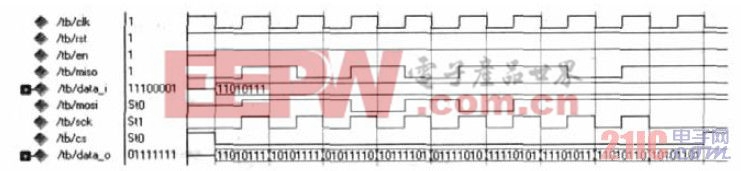

通过编写测试平台,并使用Mentor Graphics 公司的仿真工具ModelSim SE PLUS 6.1f 对该SPI 模块进行仿真,得到的仿真波形如图5 所示。

图5 SPI 模块的仿真波形

从图中可以看出,sck 的空闲电平IDLE=0,接收数据时刻是下降沿即ACTIVE-IDLE 边沿, 故该SPI 模块的工作模式是CPOL=0,CPHA=1,与设计一致。当en=0 时,cs=1,SPI 总线处于空闲状态。当en=1 时,在下降沿cs=0,sck 输出时钟信号,总线数据传输开始。同时,data_o=data_i, 移位寄存器存入待发送数据11010111.在第1 个周期上升沿,主机通过mosi 发送data_o 最高位1 至从机。在第1 个周期下降沿,data_o 左移一位,多出一个空闲位data_o[0],主机通过miso 接收从机发送的数据最高位1,并将其存入data_o[0],data_o=10101111.依此类推,后面7 个周期的数据传输过程与第1 个周期类似。8 位数据全部传输完成之后,cs=1,一个完整的SPI 总线传输过程结束。可以发现,data_o中的数据被一个一个从主机发送到从机,同时data_o 也被用来存储从机发送的数据。8 个周期完成之后,data_o 中存储的数据正是从机发送的数据10101101.综合以上分析,该SPI 模块的功能是正确的。

评论