基于改进的布斯算法FPGA嵌入式18×18乘法器

5 设计总结

5.1 综合条件说明

采用TSMC0.18μm CMOS工艺和Synopsis DC进行的综合并进行延迟分析。并在DC命令窗口输入了命令“set_dont_use”和“set_dont_ touch”。

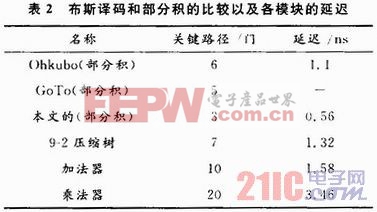

5.2 布斯译码和部分积

把传统的布斯译码和部分积与本文采取的布斯译码和部分积进行了比较,并把结果列在了表2中。从表中发现本设计关键路径与OhkuBo相比减少了50%,生成部分积的速度相应的提高了50%。

5.3 与其他的乘法器进行比较

本文的乘法器与表3中乘法器相比速度有明显提高,与Xilinx公司的Spartan-3A系列嵌入到FPGA的乘法器相比本文乘法器的速度更提高40%。更为关键的是在没有增加芯片面积的情况下把速度提高40%。

6 结语

本文基于改进的布斯算法的18×18乘法器是特意为嵌入到FPGA而设计的,它解决了乘法器占用FPGA较多资源的问题,并为以后DSP嵌入到FPGA做了必要的准备工作。采用了一种新的布斯译码和部分积、9-2压缩和两级超前进位加法器以使乘法器达到较好的性能。经过仿真验证,这里提出的基于改进的布斯乘法器各项指标均能很好的满足嵌入到FPGA的要求。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论