基于改进的布斯算法FPGA嵌入式18×18乘法器

典型的4-2压缩是由2个3-2压缩构成的,其延迟为4个异或。图3为一个优化了的4-2压缩,其延迟为3个异或的延迟。因此9-2压缩树从顶层到最终输出仅过了7个异或门的延迟。

4 35 b两级超前进位加法器

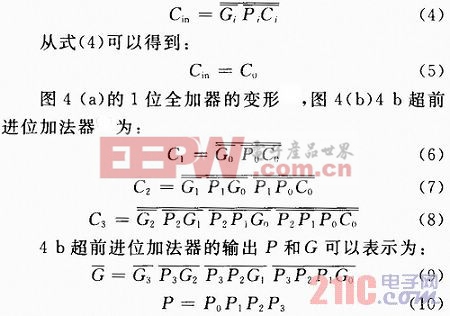

超前进位加法器对乘法器的整体性能的影响至关重要,要想提高乘法器的速度,超前进位加法器也必须进行必要的优化。在此采取基于4 b超前进位加法器的两级加法器。

由于进位链延迟时间随着输入的增加而增加,必须考虑到输入信号的个数,在面积和速度中进行折中发现4 b超前进位加法器是最适合作为基本的模块。

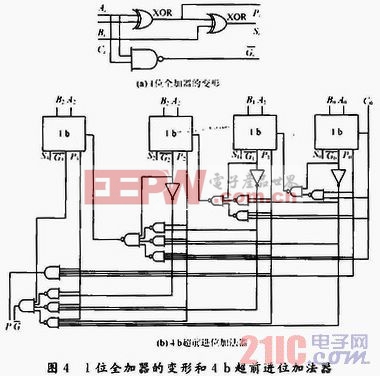

从图4(b)中可以看到在4 b超前进位加法器中,除了P和G由与门实现的,其他的都是有与非门实现的。

图4(a)为1位全加器的变形,有3个输入Ai,Bi,Ci和三个输出Pi,Si和Gi,其中Ai和Bi为两个加数,Cin为进位输入,Pi和Gi分别为进位传输和进位产生,而Si为第i位的和。

采用基于4 b的超前进位加法器来组成16 b超前进位加法器,进位链采取与4 b超前进位链相同的结构。同样的分析方法,发现16 b的P和G延时为5个门的延迟。用2个16 b的超前进位加法器和一个3 b超前进位加法器组成35 b超前进位加法器,其进位链采取与上面相同的方法。研究不难发现,经过7个门延迟进位到达3 b超前进位加法器,再经过3个门的延迟得到第35位的结果。也就是说整个加法器仅仅经过10个门的延迟。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论