基于FPGA和DSP的高速图像处理系统

2 系统硬件电路设计

2.1 图像采集模块

本系统图像采集模块采用的摄像头为CMOS图像传感器,型号为MT9M011。CMOS图像传感器与CCD传感器相比,虽然采集出来的图像效果弱差一点,但是CMOS的成本远远低于CCD产品,而且CMOS传感器的功耗较低。图像采集模块具体设计如图2所示。

2.2 图像显示模块

图像显示模块主要作用是将FPGA采集到的数字图像,实时地转换成模拟图像数据,并输出到带VGA接口的显示器上。图像显示接口电路包括图像编码电路和VGA接口电路,其电路如图3所示。本电路中选用的图像编码芯片为AD(Analog Devices)公司的高速视频数模转换芯片,其具体型号为ADV7123KST140。该芯片具有3组独立的十位宽RGB数字输入接口和3个相对的RGB模拟输出接口,5 V或3.3 V供电都行,速度为140 MHz,低功耗。本文引用地址:https://www.eepw.com.cn/article/190285.htm

2.3 DSP外部存储器接口电路设计

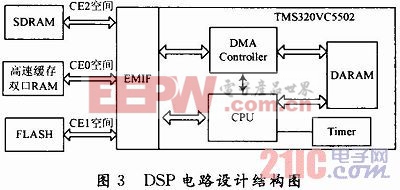

本系统中选用TI公司的超低功耗DSP(TMS320VC5502),主要是来完成图像处理算法的实现。在对外部存储器接口设计上,该DSP采用外部存储器接口(EMIF)来进行对外部存储器的扩展,具体扩展如图3所示。

TMS320VC5502的EMIF可以访问的存储空间大小为16 MB,该系统中通过配置把空间平分为4部分,EMIF的片选信号线CE3~CE0分别对应着这4个空间的选通控制。另外EMIF的组成还包括数据线D[31:0]、地址线A[21:2]、字节使能线:BE[3:0]及各类存储器的读/写控制信号线等。

fpga相关文章:fpga是什么

评论