基于FPGA的电梯控制器系统设计方案

2.2 模块设计与实现

对于分频器模块、按键请求模块、电梯控制器模块和指示模块和显示模块这四个模块,电梯控制器模块和指示模块涉及到电梯各种运行情况的处理,其算法是最复杂的,也是最容易出错的。本文采用使用有限状态机来设计该模块,具体的算法描述如下。

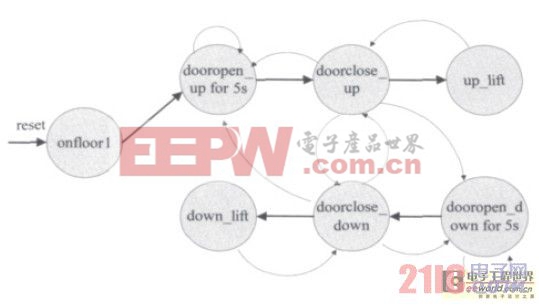

将电梯运行定义为7个状态,具体的状态定义如下:

S0:onfloor1,表示在楼层1;

S1:dooropen_up,上升过程中,电梯开门5s;

S2:doorclose_up,上升过程中,电梯关门;

S3:up_lift,表示电梯上升一层;

S4:dooropen_down,下降过程中,电梯开门5s;

S5:doorclose_down,下降过程中,电梯关门;

S6:down_lift,表示电梯下降一层。

各状态在满足一定的条件下转换,具体状态转换如图2所示。

图2 电梯控制器状态转换图

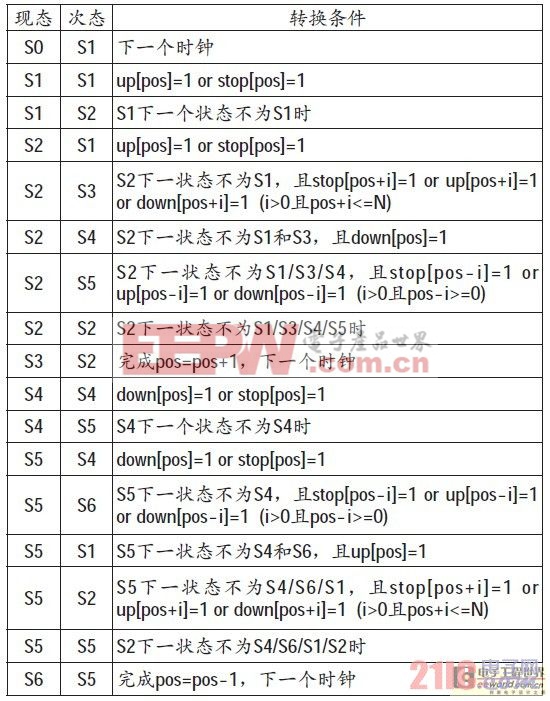

表1 电梯控制器状态转换条件

上表中, pos 表示当前楼层, up[pos ] 、down[pos]、stop[pos]分别表示当前楼层的向上、向下、和停止铵钮的状态。

显然,上述算法并未对楼层数作限制,也就是说该算法适合于任意楼层的电梯控制器。

2.3 仿真验证

本文根据上述算法,采用Verilog HDL语言在FPGA上实现了一个三层电梯控制器。对于实现来说,三层电梯或者多层电梯的控制器只是Verilog代码数量的不同,其算法则完全是本文提出的算法,没有区别。本文只所以实现了一个三层电梯控制器,是因为硬件开发环境的资源(包括按钮的数量、指示灯的数量)仅满足三层电梯控制器的验证。

评论