星载环境FPGA软件在轨重加载的一种方法

3.2 CPLD软件设计实现

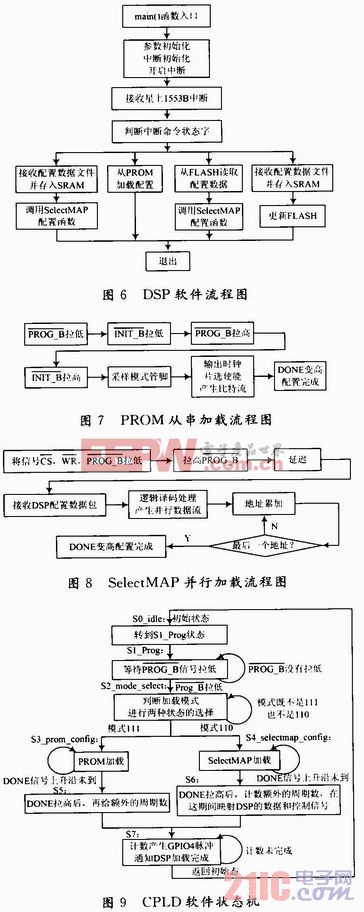

系统上电之后,DSP可以根据实际工作需要给出FPGA的两种加载方式:PROM串行加载、SelectMAP并行加载,两种方式均通过CPLD进行。

当进行PROM从串模式加载时,配置比特流从PROM中读取,具体加载实现流程如图7所示。本文引用地址:https://www.eepw.com.cn/article/190121.htm

当CPLD接到DSP发送的进行SelectMAP并行加载命令时,CPLD根据DSP端口的映射进行SelectMAP并行加载,SelectMAP加载具体实现流程如图8所示。

在SelectMAP并行加载过程中,CPLD负责在DSP和FPGA之间建立一个同步接口,将DSP传送的配置数据包进行相应的处理,生成满足Select MAP加载时序的时钟、数据及控制信号,传输至FPGA,实现对FPGA的SelectMAP加载。

CPLD软件采用了一个状态机,实现接收DSP命令进行PROM从串加载或者进行SelectMAP并行加载,状态机的流程如图9所示。

3.3 加载文件格式

对FPGA进行加载的文件格式为*.bin文件,通过bitgen产生,*.bin文件只包含FPGA配置数据,不包含任何文件信息。

4 测试验证

建立测试环境,利用测试计算机(含1553B板卡及控制软件)模拟星上控制计算机,对该FPGA重加载电

路进行测试,获得如下测试结果:

(1)在DSP软件中置PROM加载状态,上电后,FPGA从PROM加载,FPGA运行状态正常;

(2)在DSP软件中置SelectMAP加载状态,上电后,DSP从FLASH中读取配置数据,通过CPLD对FPGA进行加载,FPGA运行状态正常;

(3)在DSP软件中置SelectMAP加载状态,上电后,测试计算机通过1553B将新的配置数据传输至DSP,DSP通过CPLD对FPGA进行加载,FPGA运行状态正常。

(4)上电后,测试计算机通过1553B将新的配置数据传输至DSP,DSP将配置数据烧写至FLASH或者PROM,并置加载状态,上电后能实现新配置数据的加载。

通过以上测试表明,该电路具备FPGA星载环境下的在轨重加载功能。

5 结论

本文介绍了星载环境下通过1553B接口实现FPGA在轨重加载的方法,并完成了相应的硬件电路设计实现,通过实验室测试验证,证明本文所描述的星载环境FPGA在轨重加载方法设计思想合理可行,不仅能满足星载环境下FPGA软件的更新升级,还能实现FPGA软件功能模块的自身故障修复,并且能灵活地实现卫星应用功能的领域扩展,最大限度提高卫星系统的利用率。

评论