2.1 三线制同步串行通信控制器IP核接口描述

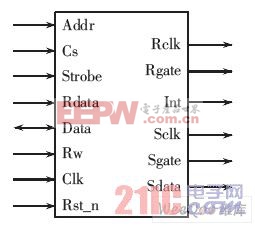

本设计最终实现的目标是生成如图2所示的IP核接口封装。

图2 三线制同步串行通信控制器IP 核接口封装图

其中,三线制同步串行通信控制器IP核接口信号定义如表1所示。该IP核共有全局信号管脚8个,接收接口信号管脚和发送接口信号管脚各3个。

表1三线制同步串行通信控制器IP核接口信号描述

2.2 三线制同步串行通信控制器IP核电路结构设计

按照设计目标,根据需要实现的功能,可将三线制同步串行通信控制器结构划分成几个大的功能模块,这些模块独自完成一定的任务,结合起来实现通信控制器的整体功能。同时,划分模块功能后,可以更方便地用硬件描述语言VHDL对其进行描述。

评论