基于FPGA的按键弹跳消除模块的研究与应用

2.2 程序设计

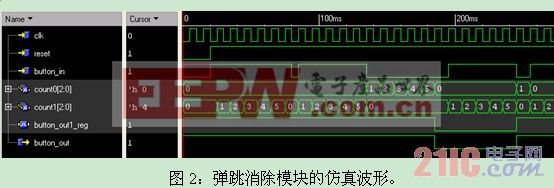

设计一个高脉冲计数器count1和一个低脉冲计数器conut0。引入一个采样脉冲信号clk,对输入信号button_in进行采样,并对clk进行计数。若button_in为高电平,count1做加法计数,直到count1各位全为1,停止计数,归零,使消抖后的输出信号button_out输出1。若button_in为低电平,count0做加法计数,直到count0各位全为1,停止计数归零,并使消抖后的输出信号button_out输出0。

部分程序如下:

module filter(clk,

reset,

button_in,

button_out);

input clk;

input reset;

input button_in;

output button_out;

wire buttong_out1;

reg [20:0] count0;

reg [20:0] count1;

reg button_out1_reg;

……

assign button_out=button_out1_reg;

//对输入进行采样,计数

always@(posedge clk or negedge reset)

begin

if(!reset) count1=21'h000000;

else if(button_out1==1'b1) count1=count1+1;//对高电平计数

else count1=21'h000000;

end

always@(posedge clk or negedge reset)

begin

if(!reset) count0=21'h000000;

else if(button_out1==1'b0) count0=count0+1;//对低电平计数

else count0=21’h000000;

end

//输出

always@(posedge clk or negedge reset

begin

if(!reset) button_out1_reg=1'b1;

else if(count0==21'h1312D0) //判断低电平信号是否符合输出条件

button_out1_reg=1'b0; //如果符合条件,则输出低电平

else if(count1==21'h1312D0) //判断低电平信号是否符合输出条件

button_out1_reg=1'b1; //如果符合条件,则输出高电平

else button_out1_reg=button_out1_reg;

end

endmodule

评论