基于FPGA的IRIG-B标准DC code编码器VHDL设计

建立一个编码器和计数器,在每个clkin时钟到来时进行计数,判断time_in的每位码值和clrin计数值确定输出脉宽,用上述同步分频模块(fenpin_e_clr)VHDL描述的方法实现输出直流码的时间起点与clr信号同步。

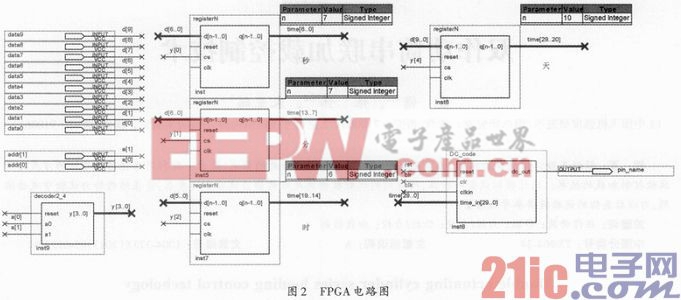

3 FPGA原理电路

IRIG-B码编码模块通过端口从外部同步接收时间码信息和准秒时刻,时间信息刷新频率为1次/s。通过一个2位地址端口,一个10位数据端口,通过地址片选依次将‘秒’、‘分’、‘时’、‘天’信息送入不同的寄存器并经寄存器送IRIG-B DC码编码器的数据输入端,由B码

编码器根据时钟生成DC码发送。其在FPGA内部实现电路原理如图2所示。本文引用地址:https://www.eepw.com.cn/article/189622.htm

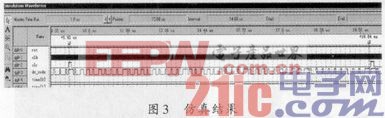

4 仿真

用QuartusⅡ建立工程文件,编辑上述代码并进行仿真,仿真结果如图3所示,输出DC码的前沿与CLR信号同步,参考标志在连续两个位置标示符后开始发送时间数据,符合IRIG-B码中直流码标准要求。

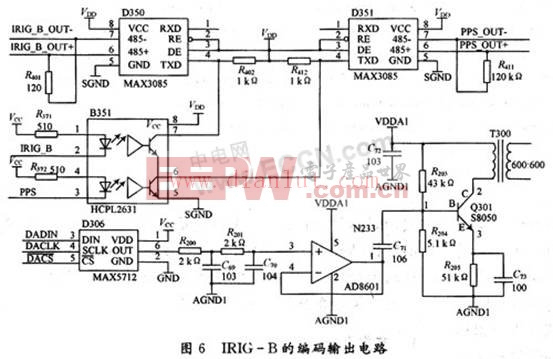

IRIG-B码是标准时间码信号。由数字处理器通过I/O向数字逻辑电路实时刷新当前时间数据(IRIG-B精确到秒),FPGA经内部逻辑电路产生标准IRIG-B(DC)码,其时间的起点与GPS时间脉冲对齐,并通过隔离差分驱动向远程提供时间信息。

5 结论

仿真和实践结果均表明,该编码器可以产生稳定、可靠、连续的IRIG-B DC码,与秒基准信号精确同步,同步误差小于1μs,已成功运用到测控设备上。

fpga相关文章:fpga是什么

脉宽调制相关文章:脉宽调制原理

评论