基于FPGA的可调信号源设计

现场可编程逻辑阵列器件(FPGA)具有编程方便、高集成度、高可靠性等优点。为了满足科研和实际测试要求,本文设计了一种以FPGA、高速D/A为核心,能产生多路频率可调信号的信号源系统。该系统中波形数据、控制命令字由上位机发出,通过FPGA控制在数据存储器中存储波形数据,并将波形数据读出送入DAC进行数模转换后得到相应的模拟信号波形及开关量的控制。利用上述方法设计的信号源,信号产生灵活、功能扩展方便、信号参数可调,实现了硬件电路的软件化设计,具有特殊的现实意义和广泛的应用前景[1]。

1 系统设计

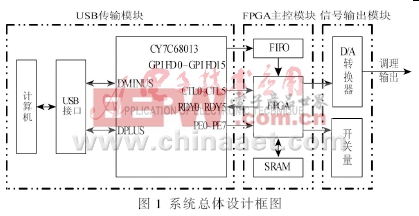

本信号源系统主要由数据输出(上位机软件)、USB数据传输接口、数据缓冲与存储(FIFO和SRAM)、控制部分(FPGA) 、数据的转换及调理(DAC、跟随器)及开关量的输出等6个模块组成。

系统总体设计框图如图1所示,其具体工作流程为:PC机发送数据至USB单片机端点FIFO,当数据大小达到512 B时,数据自动打包后送入外部缓冲FIFO。FIFO是一种先进先出的数据缓存器,它与普通存储器的区别在于没有外部读写地址线,靠空/满标志的产生来控制数据的写入与读出。在FPGA控制模块中,当FPGA接收到FIFO半满信号后,由FPGA控制将波形,数据存于SRAM中。然后FPGA控制波形数据从SRAM中取出后送D/A进行转换,经数模转换和调理电路后即得所需波形,或直接由FPGA将数据发送到继电器来控制外部供电系统的开断。

2 模块设计

2.1 USB传输部分

USB 接口即“通用串行总线接口”,是应用于计算机领域的新型接口之一,它使得外围设备与计算机的连接更加高效、便利。USB 接口不仅具有传输速率快、即插即用、支持热插拔等特点,而且易于扩展,可以有效地解决计算机外围接口不足的问题。随着在工程实际中对数据传输的速率要求越来越高,传统的串口、并口传输已经不能满足数据传输速率的要求,而USB2.0 接口最高可达480 Mb/s 的高速传输速率,使得计算机和外围设备之间的高速数据传输成为可能。同时,USB 接口设备的普及也促使其成为数据高速传输中设备连接的首选接口。

本设计考虑了两种USB2.0通信接口设计模式:(1) 基于USB 单片机的接口设计。例如以Cypress 公司开发的CY7C68013 单片机为控制核心而设计的USB 通讯接口;(2)基于协议转换芯片的接口设计,例如以FTDI 公司推出的FT245BM 协议接口芯片为控制核心的USB 通信接口。

(1)USB-单片机

CY7C68013单片机[2]的GPIF接口有16位数据线、6个RDY信号和6个CTL信号。RDY信号用于对输入的信号进行判断, CTL用于输出对外部器件的控制命令,16位数据线用于单片机与外部器件进行数据交换和传输。该芯片集成了51单片机内核、USB2.0收发器、串行接口引擎(SIE)、4 KB FIFO存储器以及通用可编程接口等模块,这些模块保证了CY7C68013与DSP、ATA等外围器件实现无缝、高速的数据传输。

(2)USB-FIFO

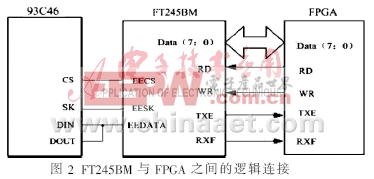

FT245BM是由FTDI公司推出的USB协议芯片。FT245BM内含2个FIFO数据缓冲区。一个是128 B的接收缓冲区,另一个是384 B的发送缓冲区。它们用作USB数据与并行I/O口数据的交换缓冲区。FIFO是实现与外界(微控制器、FPGA或其他器件)数据互换的接口,它主要通过8根数据线DO~D7、读写控制线RD和WR以及FIFO发送缓冲区空标志TXE和FIFO接收缓冲区非空标志RXF来完成数据的交互。FT245BM与FPGA之间的逻辑连接图如图2所示。

评论