三相交错式双向DC/DC储能变流器的研究

3 三相交错PWM驱动波形的产生方式

该变流器数字控制系统采用DSP作为主控器,通过配置DSP内部事件管理器(EV)的各寄存器,可产生6路互不干扰的PWM驱动波形。双向

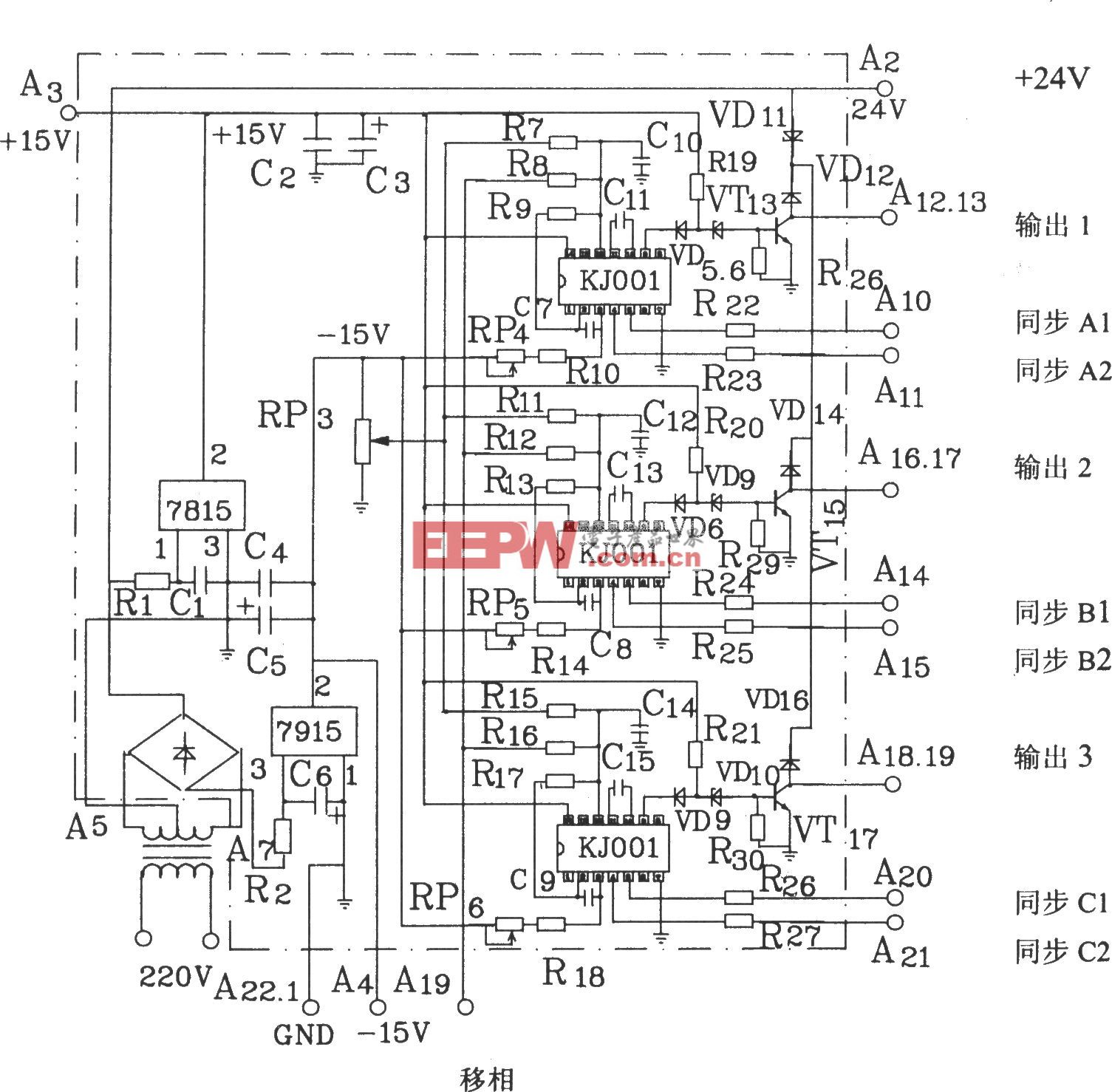

DC/DC变流器可工作在独立PWM和互补PWM两种模式下,在此选择独立PWM工作方式。即当系统工作在Buck模式时,仅上桥臂功率管工作,所有下桥臂功率管可靠关断;当系统工作在Boost模式时,仅下桥臂功率管工作,所有上桥臂功率管可靠关断。由于EV基于同一个时钟信号产生PWM驱动波,各PWM波同相位,需要经过移相才能应用于三相交错变流器系统。在此采用FPGA内部FIFO存储器实现PWM波形移相功能。

在QuartusⅡ中,FIFO模型可用MegaWizard创建,也可用HDL代码创建,两种创建方式实际都是对存储器进行参数配置的过程,在此选用

VHDL语言创建该模型。该系统设定功率管开关频率为5 kHz,因此DSP应产生周期为200 ms的PWM驱动波形,对其进行60°和120°移相,实际就是进行200/3 ms和400/3 ms的延时。选用频率为33 MHz的FPGA,FIFO数据读入读出的频率直接使用系统频率,若要产生200/3 ms的延时,FIFO压栈深度应该为2 200,若要产生400/3 ms的延时,FIFO压栈深度应该为4 400,因此配置FIFO最大压栈深度为8 192,对应地址宽度为13。系统Boost,Buck驱动波形相互独立,FIFO位宽设置为2,分别实现Buck与Boost驱动波形的移相。

配置两个FIFO模型FIFO1与FIFO2,分别设置两个计数变量,使得FIFO1读使能滞后写使能2 200个系统时钟周期,则产生60°波形移相;使得FIFO2读使能滞后写使能4 400个系统时钟周期,则产生120°波形移相。最后需要对FIFO模型进行端口映射,其输入映射到DSP的PWM输出端,输出映射到PEBB模块驱动输入端,复位信号端映射到DSP输出移相使能端。当输出使能端有效时,FPGA对三相驱动波形进行相应移相,系统工作在三相交错模式;当输出使能无效时,FPGA直接输出一相原始波形,系统工作在单相模式,如此可以轻松实现两种模式的切换。

4 实验结果及分析

根据上述模型搭建实验平台,PEBB选用IGBT模块。直流输入由三相调压器通过三相整流桥整流得到,Boost模式下模拟蓄电池放电;负载为50 Ω大功率电阻,Buck模式下模拟蓄电池充电。

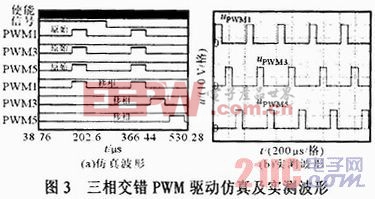

图3示出系统Buck模式下三相PWM波形移相QuartusⅡ仿真结果与实测结果。分析波形可知,三相驱动波互差60°,误差在30 ns以内,完全符合设计要求。本文引用地址:https://www.eepw.com.cn/article/177581.htm

评论