CDMA 2000系统中前向链路卷积编码器的FPGA实现

在卷积码的编码过程中,编码器从全零状态出发,最后必须回到全零状态,故当送完信息后,还要向编码器再送入K-1段全零信息,以迫使编码器回到全零状态。设此编码器的起始状态为零,即b1b2b3为000。当输入的信息位为11010时,为保证输入的全部信息位都能通过移位寄存器,并对移位寄存器进行复位,必须在信息位后加约束长度减一个零,即两个零;此时对应的输出码元序列为:10111001011100,丢弃后四位可得编码器的输出信息:1011100101。整个工作过程中编码器的状态如表1所示。本文引用地址:https://www.eepw.com.cn/article/172582.htm

1.2 CDMA 2000系统中的前向链路卷积编码器

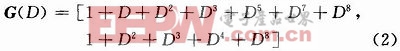

在CDMA 2000系统中,前向链路使用编码率为1/2,约束长度为9的卷积编码器。前向链路卷积码的生成多项式矩阵为:

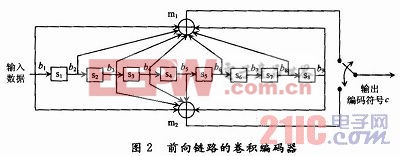

由此生成多项式矩阵可得前向编码器的结构图,如图2所示。图中s1~s8为移位寄存器;m1,m2为模2和加法器;其中b1代表当前输入的信息位;移位寄存器状态b2~b9存储以前的信息位;c代表编码后的输出码元。

评论