基于FPGA+MCU的大型LED显示屏系统设计

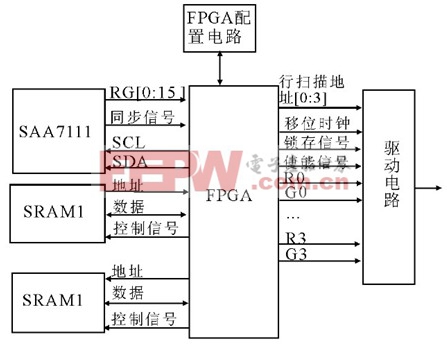

FPGA的硬件设计如图3所示。FPGA 需要提供大量的I/O引脚和高速的显示控制信号,所选用的基于Xilinx公司的FPGA 的90nm 工艺制造的XC3S250E-FTG256可以满足设计的要求。

图3 FPGA的硬件结构

2.3驱动电路

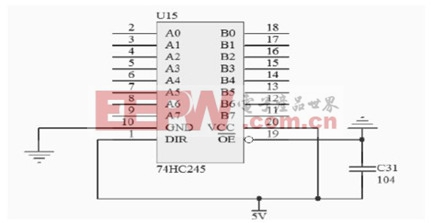

FPGA采用的电压是3.3V,而LED屏体显示电路的电压是5V的TTL逻辑电平,因此需要进行电平转换的电路。这个电路由74HC245构成,工作电压为5V,74HC245采用CMOS工艺,是一种三态输出、8组总线收发器,其输入电平兼容3.3V系统,使用外接的5V电源将输出电平提升到5V,同时为各种控制和数据信号提供驱动能力。74HC245的电路如图4所示。其中:OE为输出控制引脚,低电平为有效;DIR引脚用于控制转换方向,接高电平时表示从A向B转换,A0~A7用于输入数据信号,B0~B7用于输出转换后的数据信号。

图4 74HC245驱动电路

2.4显示板的驱动电路

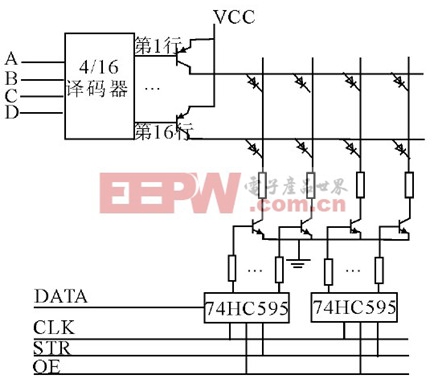

LED显示板的面积很大,它的正面由LED 显示块级联而成,背面是驱动电路。由于LED的驱动电流相对较大,驱动电路应尽量和LED点阵模块靠近。因此行列驱动器一般都安装在屏体的背面。LED显示板的驱动电路中采用了74HC595芯片,是硅结构的CMOS器件,兼容低电压TTL电路,具有8位串入并出的移位、并行锁存和三态输出功能。移位寄存器和锁存器使用独立的时钟,数据SDATA 在SCLK的上升沿输入移位寄存器,在LT的上升沿进入的锁存器中去。当使能信号OE为低电平时,锁存器的数据输出到LED.74HC595芯片可以解决数据显示和数据串行传输在时间上的冲突问题,在显示1行各列数据的同时,可以准备下1列的LED数据。以1/16行扫描为例,LED显示板的驱动电路如图5所示。

CLK是移位寄存器时钟,每个脉冲将引起1位数据移入74HC595中,当1行的数据全部移完后,锁存信号LT控制数据从74HC595的寄存器移入锁存器。A、B、C、D是行扫描信号,其中A是最低位,通过4/16译码器控制LED屏的行扫描。OE是消影信号,它可以选择控制行信号或列信号,用于LED点阵是否能被点亮和控制整屏的亮度。如果OE控制列信号,它接74HC595芯片的OE端,因为只有当OE为低电平时74HC595的输出才有效,否则输出三态。如果OE控制行信号,它接到4/16译码器的使能端,低电平时行扫描不起作用。

图5 LED显示板的驱动电路

评论