基于TMS320C6713B的实时数字视频消旋系统设计

2 系统硬件设计

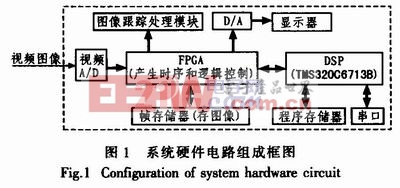

实时数字视频消旋系统主要有4部分组成:视频A/D、DSP、FPGA和帧存储器。图l是系统硬件组成框图。其原理是外界图像经A/D采样为数字图像进入FPGA,FPGA将图像写入帧存储器中,DSP根据上位机通过RS-232串口送来的角速度值,计算新图像各点在当前帧图像中的位置,将计算后的位置送给FPGA,通过FIGA做地址映射,再将图像按映射后的地址输出送D/A显示或送跟踪处理模块进行目标跟踪识别等处理。

2.1 TMS320C6713B数据处理单元

在本方案中DSP是数据处理的核心,主要是通过串口读取上位机送来的图像旋转的角速度信息,根据该信息进行仿射变换,求出旋转后的图像各点在原图像中的坐标,并将求出的坐标写入FPGA。在计算图像精确位置时需要进行大量的浮点运算,需要具有高速高精度浮点运算能力的DSP。方案采用了美国TI公司的高性能浮点数字信号处理器TMS320C6713B。它采用先进的超长指令字结构,为单精度(32位)和64位(双字)的IEEE浮点操作提供硬件支持,且32位整型乘法可以获得32位或64位结果。其内部有8个独立的功能单元,2个定点算术逻辑单元(ALU),2个浮点乘法器,4个浮点ALU,每个周期可以执行8个32位指令。内部设计有32个32位通用目的寄存器,4 K字节的L1高速程序缓存器和4K字节的L1高速数据缓存器,256 K字节的L2两级数据缓存器。这种结构设计可以最大限度发挥8个功能单元的并行运算能力,使得DSP在300 MHz系统时钟工作时,其运算能力最高为2 400 MIPS,浮点运算能力最高为1 800 MFLOPS,极大地满足了高速数据处理的要求。

另外,DSP6713B片内还提供多种集成外设:多种复位加载模式(BOOT)、多通道DMA控制器、多通道缓存串口(McBSP)以及能够与SDRAM、SBSRAM或异步存储器直接接口的高性能外部存储器接口(EMIF),这些都为数据处理带来了极大方便。

2.2 FPGA模块单元

方案采用了Actel公司推出的第二代基于Flash(闪存)的可编程器件ProASIC Plus系列中的APAl50。该系列器件兼具ASIC(专用集成电路)的性能和FPGA的灵活性于一身,具有150 000个系统门,逻辑单元为6 144个,内嵌36KB的双端口SRAM和2个锁相环(PLL)内核,支持3.3 V、

32 bit、50 MHz的PCI总线,系统外部性能可达150 MHz,具有高密度、低功耗、非易失及可重复编程等特点。因为ProASIC Plus系列FPGA基于Hash技术,利用Hash开关保存内部逻辑,因此不需要另外的器件。由于不需要上电配置过程,因此具备上电就立即工作的特点。另外高度保密,使用者可编程设置多位密钥以阻止外界自行读取或更改器件的配置。

方案中利用APAl50主要实现逻辑控制、A/D采样控制、D/A显示控制、向帧存储器写图像以及完成旋转后的图像与原始图像的地址映射等功能。

评论