某伺服PWM驱动系统中低通功率滤波电路优化设计

如图7所示,以交流方式分析总体效率与频率关系,效率即输出有效功率与输入有效功率之比,在扫描频率段内效率仅2%的变化,大部分频带内仍有86.7%以上的效率。其中60 Hz左右的效率骤降是由于直流峰值功率向交流有效值功率的瞬态改变而引起的数学计算差。

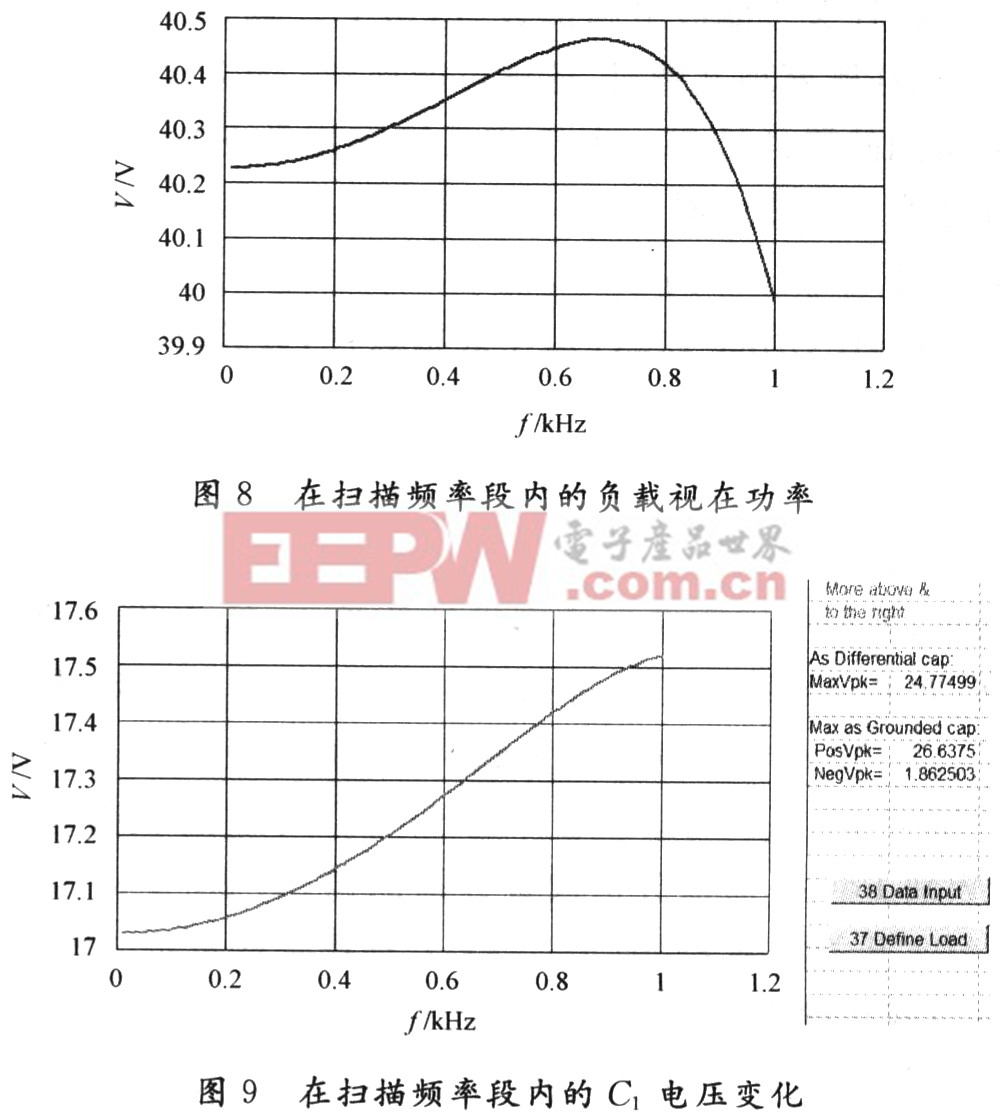

如图8所示,随着频率增加,负载上的视在功率增加的比例不大,通过其他图表的研究,发现增加是由于负载上的电流和电压随着频率有所增加,如果对最终输出有很大影响的话,可以在电路中设置一个简单的可调增益来补偿该点。

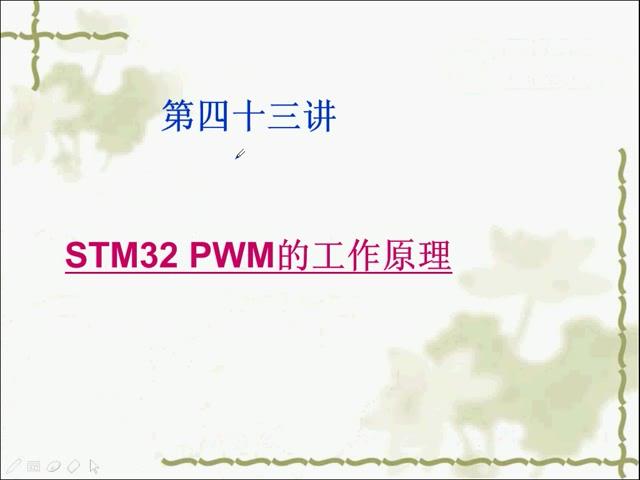

如图9所示,软件可以通过频率扫描分析计算各元件的应力值,图中显示了C1的3个峰值电压,电容上的压差是24.77pk,接地电容的峰值电压是26. 64 V和1.86 V。在这个设计中C1无需双极性电容,但在某些设计中,峰值可能会出现负值,此时必须使用双极性电容。

如图10所示,滤波电路会带来相位移。当反馈信号直接从PWM放大器的输出端采样时这常不是问题,然而在该伺服平台设计中,反馈从滤波电路后面取,会引入相位移,影响系统的相角裕度,图10显示了负载中电压和电流的相位移,如果对最终输出有很大影响的话,可以增加Fmax和Fcutoff的分频比例,相位移将会减小,除此之外减小滤波电路的级数也会减小相位移。

DIY机械键盘相关社区:机械键盘DIY

pwm相关文章:pwm原理

评论