CMOS伪差分E类射频功率放大器设计

2 射频CMOS E类功率放大器非理想因素分析

分析了理想功放的设计方程,有载QL的选择,负载网络元器件的选取等,但是这些理论基础都建立在理想情况下,而在实际设计中,必须考虑非理想的因素。非理想因素有多种:

(1)寄生电感的影响。

(2)有限的Chock电感。

(3)NMOS开关管有限的导通电阻。

(4)NMOS管寄生电容Cd的非线性。

(5)负载网络的有限Q值。

(6)功率放大器阻抗匹配网络的损耗。

其中寄生电感对功放的设计结果影响最大,因此将着重分析寄生电感的产生及其改进措施。

寄生电感分析与改进措施

功率放大器在实际应用中有3个主要的寄生源,分别为RF电路板、封装和IC。具体表现在输出级源级到地的寄生电感,它对功率放大器的输出功率、PAE、稳定性等产生巨大的影响。寄生电感可以分为以下3个方面:

(1)在IC级,功率放大器一般用通孔结构或者键合线联接到衬底地。在实际应用中,可使用多线键合减小地电感。

(2)在封装级,通常用接到封装底部的接地片,或通过封装引线架的地连接实现接地。可用各种方法调整引线架,以减小地电感。

(3)在RF电路板级的地连接一般用通孔接到电路板中间层的专门接地平板。接地的质量由物理特性和与系统地的连接好坏确定。

接电源(地)的封装线对电路的影响与高速电路中同步开关噪声原理相似。交流电流在封装线上引起的感应电势为

其中,Le为电源和地封装线的总等效电感。假设当Le=1 nH,交流电流幅度i为300 mA时,即可达300 mV,如果电感和寄生电容发生谐振,振荡信号的幅度会更高,必然会对输出信号形成干扰。电源(地)封装线对电路的另一影响是信号或其谐波可能引起振荡,这些影响是很难通过在电源和地之间接并联大耦合电容得到抑制的。因此采用合理的电路结构才能减轻寄生电感对系统的影响。

3 射频CMOS E类功率放大器设计

功率放大器的输出级是电路最关键、最复杂的部分,因为它的输出是芯片射频接口,除了器件的非线性特性外,还必须要考虑Pad、输出功率管漏端到地的寄生电感、封装结构、输出电压摆幅、MOS器件击穿和输出端口的阻抗匹配等多种因素的影响。在这些因素中,输出功率管漏端到地的寄生电感对功放性能影响最严重,包括键合线电感、PCB板级电路寄生电感等的影响。键合线电感的经验值是1 nH/mm,可以并联大量的键合线来减少键合线电感值,但是很难控制其精度,有文献在仿真时仅加入0.4 nH的电感模拟这些寄生量,但是从测试结果分析来看,寄生电感远不只0.4 nH,因此取1.5 nH来模拟功率管源端到地的寄生电感量。

3.1 应用理想方程的功放级设计

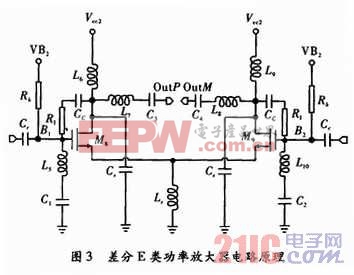

功放内核电路如图3所示,采用伪差分E类功率放大器,为简化分析过程,分析右半边电路图,L5为片上平面螺旋电感,L6,L7,Ls为键合线电感。输出级为E类功放,Choke电感L6阻止交流信号通过,并给晶体管提供直流电流Idc。反馈网络Cs和Rs增强功率放大器的稳定性和降低输出电压驻波比。 L7、C3组成一个串联LC网络,包括一个谐振网络和部分剩余电感,当该谐振网络的品质因子足够高时,流过该网络的电流为理想的正弦型信号,所有的谐波成分都被滤除。并联电容Cs由两部分组成,一部分是晶体管的寄生电容,另一部分是实际引入的电容。

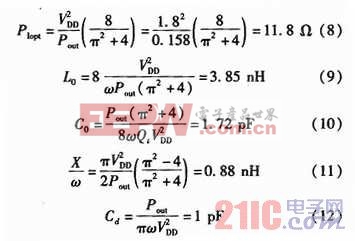

在设计之初,先利用理想设计方程,估算E类功率放大器的各个参数,再采用谐波平衡法(Harmonic Balance)适当地调整参数。其中Pout=24 dBm,电源电压VDD=1.8 V,取Qt=5,根据之前给出的设计方程得出本文引用地址:https://www.eepw.com.cn/article/162561.htm

以上参数选取依赖于理想设计方程参数,只考虑到最佳负载为实部的情况,考虑到一些非理想因素,利用ADS软件,采用Load Pull技术适当地调整参数。

3.2 应用Load Pull技术的功放级设计

在功放级设计中,如何使输出功率最大化是最主要的设计目标。

基本思路是通过CAD技术进行Load Pull仿真确定最佳的源和负载阻抗。所谓的Load Pull仿真,就是在负载阻抗很大范围内扫描,逐点作谐波平衡分析计算出输出功率,在圆图上画出等功率圆。因此根据设计目标的输出功率,就能在圆图上找到与之对应的一系列的输出阻抗。同样的原理,可以画出等PAE的圆,折中考虑输出功率,PAE和负载网络的有载QL等就能确定最佳阻抗。

评论