一种简易的超宽带纳秒级脉冲发生器设计

2 纳秒级脉冲信号的产生

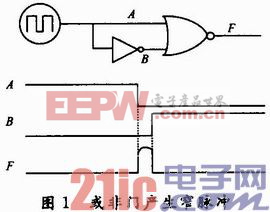

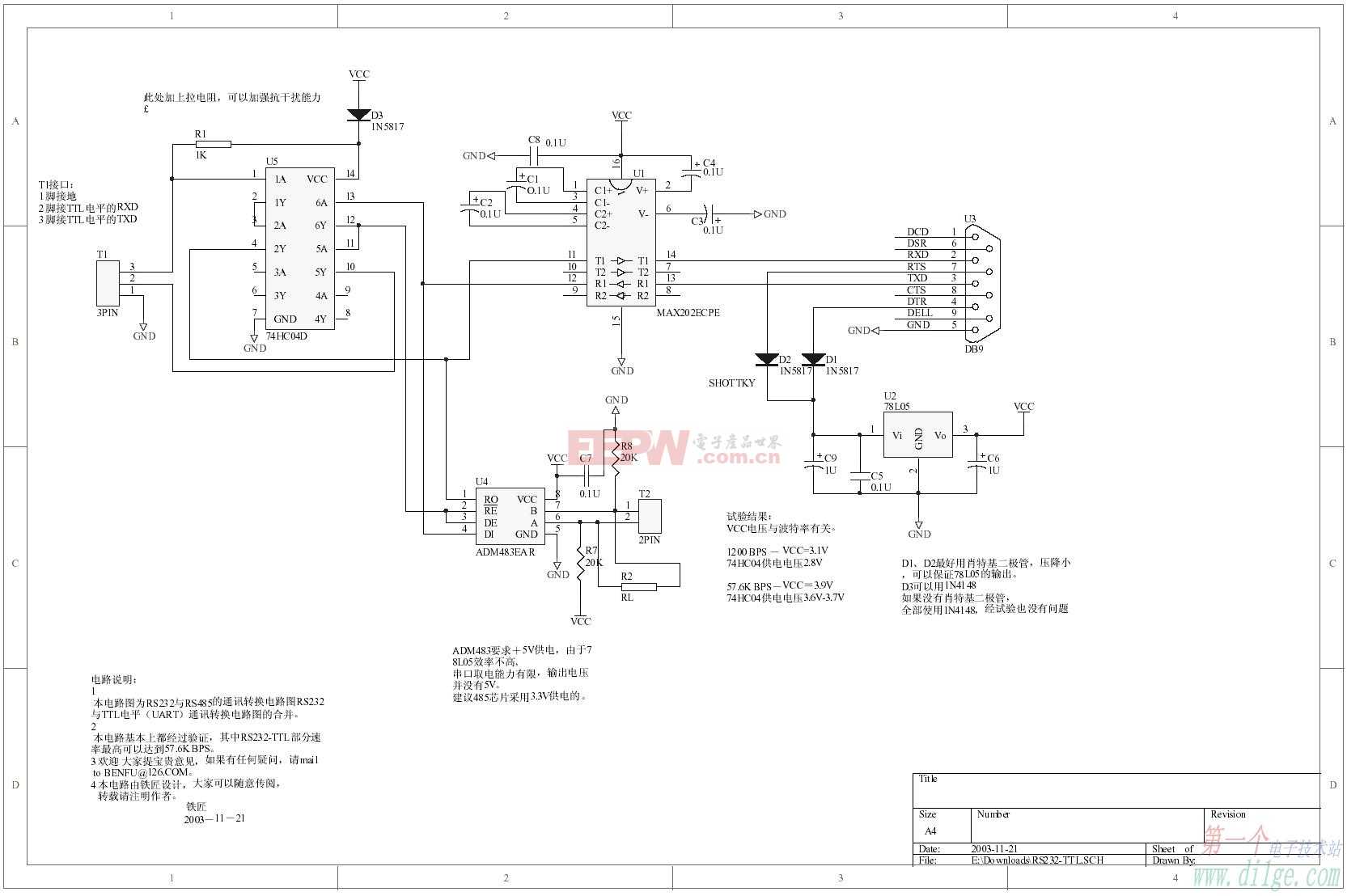

本设计采用数字电路的逻辑特性来产生纳秒级窄脉冲信号,然后利用微分滤波产生更适合无线信道传输的UWB波形。基于数字逻辑器件产生窄脉冲主要利用的是逻辑门电路的竞争冒险现象来完成。文中采用两输入的或非门来产生窄脉冲,如图1所示。其逻辑表达式为:

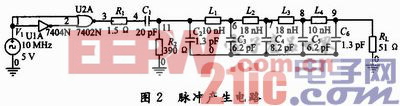

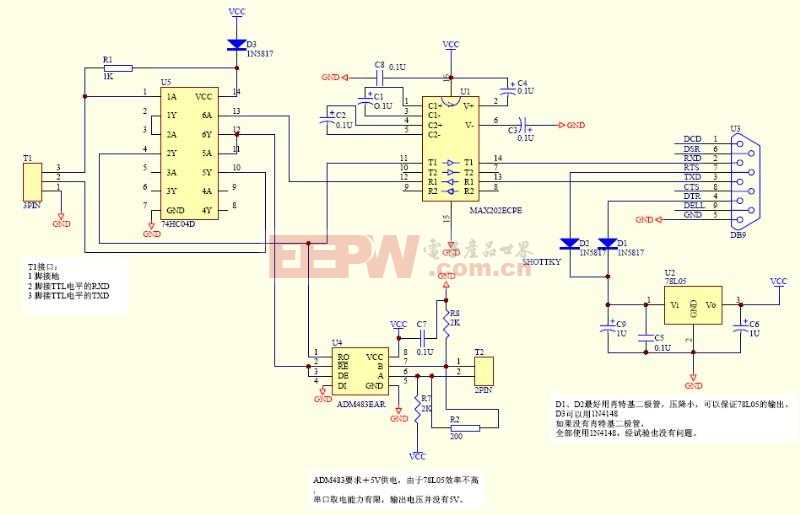

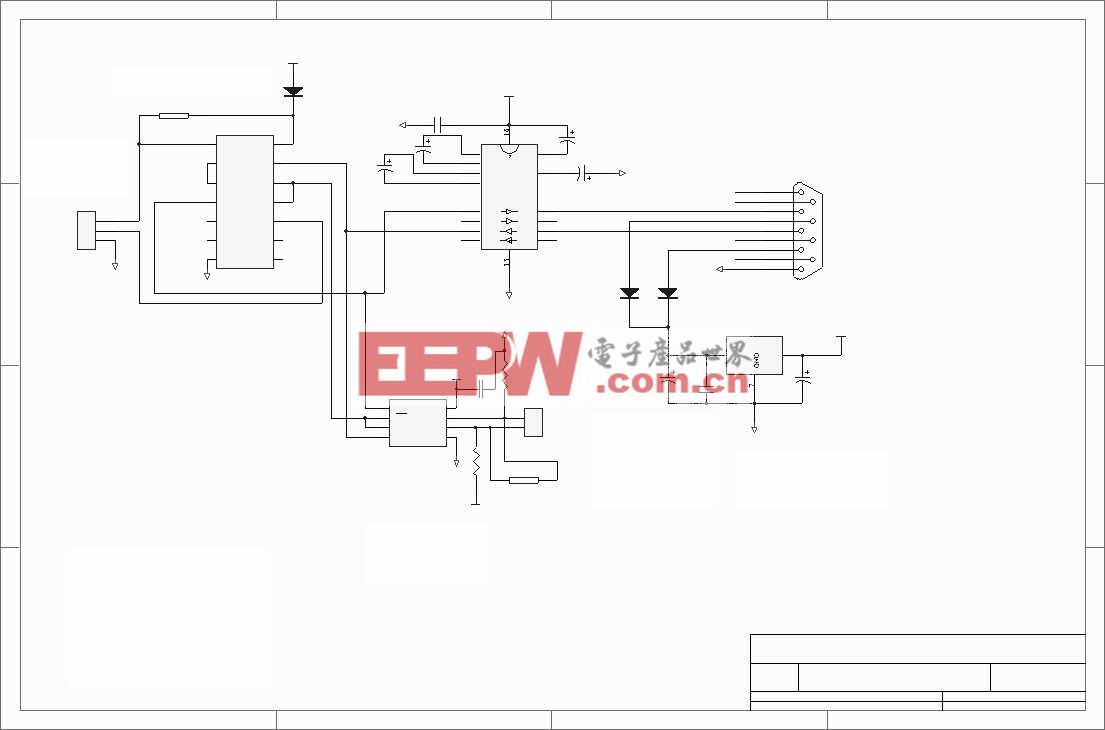

对于TTL器件来说,其产生的窄脉冲近似钟形,类似于高斯函数波形,通过合理组合RLC元件,就可以产生类似于一阶高斯脉冲函数。电路图如图2所示。

首先时钟信号是由10 MHz晶振电路产生,其输出分别输入到74HC04和74HC02的一个输入端。输入74HC04的时钟信号经过非门产生一个极性相反、有足够陡峭的上升沿和幅度的信号,并将其输入到74HC02的另一个输入端。由或非门产生一个窄脉冲。后端的微分滤波电路主要完成脉冲的成形,通过调整RLC的参数,就可以得到合理的脉冲波形。其中脉冲延时时间主要由74HC04非门的平均传输时延决定,需要注意的是,由于是高速脉冲的传输,所以电路的布线也会影响脉冲的延迟时间,所以信号的布线应考虑成传输线。

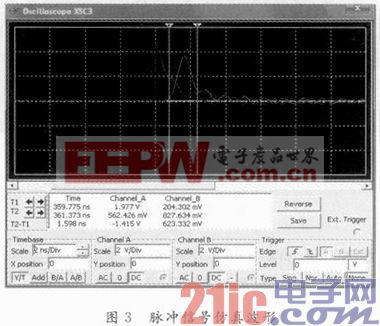

使用Electronics Workbench Multisim 10.O软件来对电路进行仿真。仿真波形如图3所示。其结果可得到重复频率为10 MHz,脉冲幅度为3.59 V,脉冲宽度为1.5 ns的窄脉冲。

评论