基于FPDP的高速数据传输系统设计

FPDP接收逻辑接收来自A/D板的回波数据,主要负责对数据缓冲区FIFO的写入操作。其工作流程如下:在FPDP总线数据有效(DVALIDn为低)时,FIFO的写请求Wr-req信号有效,此时数据随着写时钟信号(Wr-clk即AD板发送过来的Ad-strob信号)写入FIFO。若FPDP总线数据无效,此时FIFO的写请求信号也无效,数据不能写入FIFO。

FPDP发送逻辑接负责将回波数据和其他飞机参数按照一定的格式打包,并经由FPDP总线发送出去。其工作流程如下:FIFO的读请求Rd-req信号由发送时序计数器产生,当计数器的计数值为一定值(A/D采集满一帧数据)时,Rd-req有效,随着读时钟(Rd-clk即A/D板时钟AD_strob)信号,数据从FIFO中读出,此时计数器清零。数据按一定格式打包后,按FPDP单帧传输模式将打包数据送入DSP板。

FPDP发送逻辑应当在FPDP同步信号SYNCn到来后立即启动数据发送,这样大大增强了数据传输的实时性和可靠性。值得注意的是,A/D板传来的第一组回波数据来不及打包传送给DSP板,因此要在FIFO中累积一组回波数据后再开始往DSP板发送数据,这样每次发给DSP板的一帧数据中,回波数据应为上一次A/D板发来的数据,这样可以保证不丢失回波数据,只是最后一组回波数据仍然会存在于时序板中,采集不到,应当丢弃。

特别地,由于模块的输入输出功能已确定,所以作为A/D板接收端的方向信号DIRn不被使用,而作为DSP板发送端的DIRn信号则常接低。对于输入的SUSPENDn和NRDYn信号,A/D采集板对NRDYn信号不响应,所以FPGA对这两个信号也不响应,避免干扰AD采集板的数据采集。本文引用地址:https://www.eepw.com.cn/article/152271.htm

3 设计仿真

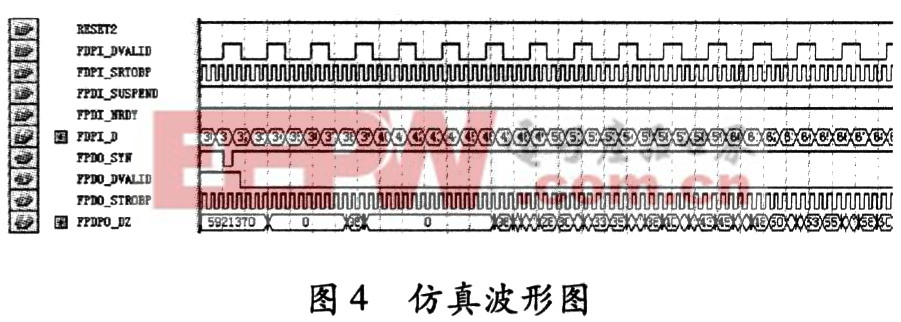

以下给出了基于Quartus 6.0的一段波形仿真图,如图4所示。

如图4所示,为FPDP发送逻辑的仿真图,其中FPDI_SUSPEND和FPDI_NRDY始终无效(为高),在发送数据前FPDO_SYN先有效(为低),此时FPDO_DVALID仍无效(为高)。在传输数据时,FPDO_DVALID有效(为低),在时钟FPDO_STROBP的上升沿将数据通过FPDP总线送出。

4 结束语

从以上的分析得出以下结论:

(1)该设计中,FPDP总线以其特有的前面板方式和传输机制,有效地解决了多块板卡间的高速数据传输问题;

(2)FPDP数据的高速、实时接收和发送是难点。该设计采用了一个片内FIFO缓冲区解决了此问题。片内FIFO集成度高、占用资源少,有效地解决了系统需求;

(3)该设计使用同步信号作为接收帧的有效标志,提高了系统的实时性和可靠性。

评论