基于FPGA的PCIE总线扩展卡的设计

控制区域中含有一些控制信息,其中第16位用来控制传输方向,为O是DMA写,为1是DMA读,这里的读/写是以主机端为参考的,如果以PCIE核为参考,方向刚好相反。第18位用来使能DMA传输计数,如果该位使能为1,那么在DMA传输过程中,PCIE核每完成1次DMA操作,都会进行1次计数操作,然后把这个计数结果传送给主机,主机把这个结果填写到描述符表的RCLAST字段中。

表大小是指本次链式DMA操作对应的描述符个数,每个描述符对应一次DMA操作。

RCLAST是一个计数单元,它有两个作用,在链式DMA传输前,表示还有多少个DMA操作等待传输,由于它是从0开始计数的,所以这个值等于表大小减1。还有一个重要作用是在链式DMA传输过程中,用来表示链式DMA传输的状态。如上所述,如果控制区域的第18位设置为1,那么每完成1次DMA操作,主机都会更新这个计数器。当计数器的数值(也是从O开始计数的)等于前面设置的期望传输的DMA次数,就表示链式DMA传输操作结束。开发人员可以用这个状态单元来察看本次传输是否结束,从而开始一个新的传输周期。

DMA长度用来设置本描述符对应的DMA传输的长度,是以32位为单位的。主机端地址用来指示数据存放存放的位置。

3. 2 实现范例

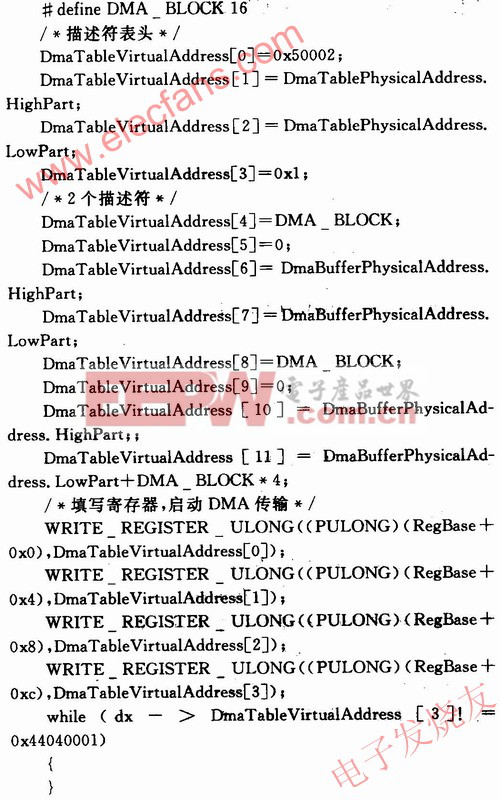

根据上面介绍的描述符表,下面给出一个链式DMA读的驱动程序例子。首先生成一个描述符表,然后把描述符表表头的4个字段的内容分别写入BAR2地址偏移量为0x0,0x4,0x8和0xC寄存器中。写完后即开始此次链式DMA读传输,while循环用于等待链式DMA结束。从下面的代码可以看出,2个描述符对应2次DMA操作。

评论