基于FPGA的数据采集板设计与实现

30MHz的线性调频信号, 设计系统时M 值取为2,则时钟设计所定的fs = 40 MHz, 通过FPGA实测得到中频采样数据, 如图2所示。

图2 FPGA实测中频采样数据

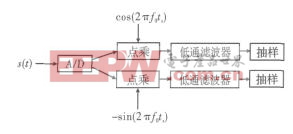

对中频实信号进行采样后, 下一步是进行数字混频和滤波处理, 使信号变为零中频正交信号(零中频正交信号即是回波信号的复包络, 包含了回波的所有有用信息) , 即为数字下变频, 其作为雷达信号处理中的关键技术之一, 这里采用低通滤波法来实现, 低通滤波法包括正交插值、低通滤波和抽样3个部分。数字下变频的算法框图, 如图3所示。

图3 数字下变频算法框图

相比于传统的模拟处理方法, 本方法从根本上解决I, Q两路正交误差和幅度不平衡, 提高了镜频抑制比。

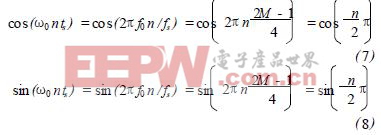

其中混频, 即点乘的实现, 根据中频带通采样定理有

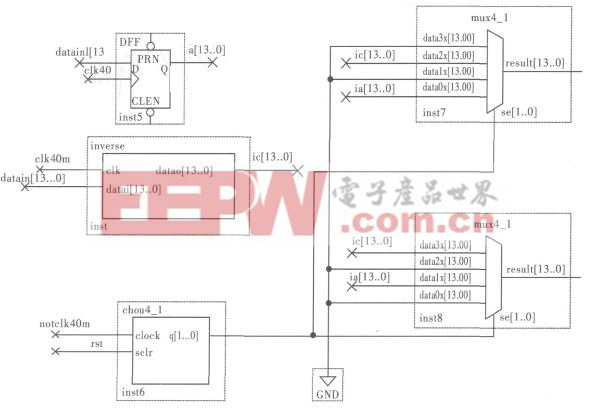

这是以{1, 0, - 1, 0}和{0, 1, 0, - 1}为周期循环的两个序列。当外部数据进来时根据不同时刻输出不同的数据, 主要包括原值、原值取反和0。其FPGA实现电路, 如图4所示。

图4 数字混频的FPGA实现电路

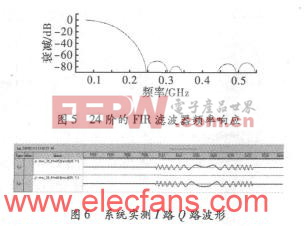

在整个正交相干检波过程中, 除了ADC的量化影响外, 整个正交检波系统的性能, 由低通滤波器的设计决定。由于镜频分量处于滤波器的阻带, 因而阻带衰减决定了镜频的抑制程度。文中采用的低通滤波器为24阶F IR滤波器, 其阻带衰减> 70 dB镜频分量得到了较好的抑制 。24阶FIR滤波器的频率特性, 如图5所示。

输入时宽带宽积为55的线性调频信号, 实测的I路与Q路波形, 如图6所示。

评论