基于FPGA的语音端点检测

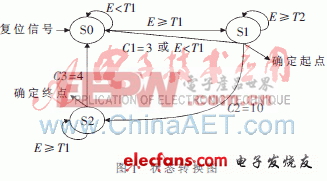

具体判断过程为:(1)在S0状态下,E

2 实验结果

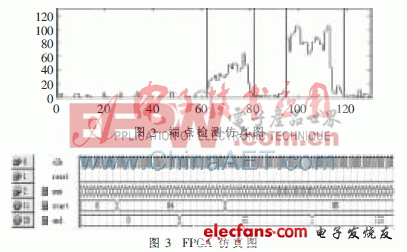

实验时的声音样本采用电脑声卡采集(16 kHz,8 bit)的“wav“文件, 并对常用的词语进行实验。图2是词“长沙”在Matlab上的端点检测仿真结果图,其中横坐标代表帧号、纵坐标代表帧能量。两个字的语音段分别是64~82帧和95~120帧。图3是词“长沙”在QuartusⅡ上仿真的结果图,其中num代表每帧的帧号,start代表语音开始的帧号,end代表语音结束的帧号。从图1、图2可以看出词“长沙”的端点检查仿真结果在Quartus Ⅱ上的和Matlab上是一致的,从图中可以看出改进后的端点检测方法检测效果非常好。

本文在加窗的过程中合理地运用了DSP Builder工具,简化了硬件的设计,同时也加快了处理速度,是一种很值得借鉴的FPGA加窗方法。在端点判断的算法上,用改进的Lawrence Rabiner端点检测法,对算法门限的计算和起止点判断做了改进,并用有限状态机实现了FPGA的设计,实验证明该算法在低信噪比的情况下能准确地找到语音信号的起止点。与其他一些端点检测方法相比,该算法更加简单、稳定,所需的存储空间小,是一种理想的硬件端点检查方法,对语音识别系统的开发和设计有一定的参考价值。

评论